摘要:前导1判断模块是浮点加法运算中不可缺少的部分, 在运算结果产生之前就对运算结果进行预测的方式叫做前导1预判, 相应的电路叫前导1预判电路。经过改进的双通道前导1预判电路与单通道运算结构相比具有更高的运算速度, 而全定制的版图设计方法具有减小单元面积和时延的优点, 用全定制版图设计的方法来设计双通道前导1预判模块, 能够进一步提高其性能。

关键词:浮点运算; 前导1; 双通道; 旁路逻辑; 全定制; 版图设计

Abstract:The leading-one prediction is part of the floating point adder.The leading-one prediction algorithm is based on leading-one prediction. The position of the loading-one can be predicted by two paths, and for some operators, the speed of operation can be accelerated and the power consumption can be lower. The full-custom layout design can potentially maximizes the performance of the circuit, and minimizes its area.

Keyword:floating-point eading-one; two-path; bypass-logic; full-custom; layout design;

引言

前导1预判电路是浮点运算中不可缺少的一部分, 其原理是将先导1位置的判断与加/减法运算同步进行, 而不必等到加/减法运算完成以后再根据其结果进行判定。在运算速度上, 采用前导1预判电路的浮点运算单元比采用前导1判定电路的单元具有更大的优势。在前导1预判电路中, 通过增加一个通道可以减少部分操作数的预判时间, 进一步提高电路的运算速度[1].全定制版图设计方法具有减少版图面积和时延的优点, 将全定制版图设计方法用于双通道前导1预判电路中, 能够进一步提高电路的性能。

1 双通道前导1预判模块的原理[1]

浮点操作数都是规格化数, 在浮点减法运算中, 当有借位的情况发生时, 先导1的位置是不确定的, 这就需要使用预判模块来进行判断。, 而在浮点加法运算中, 先导1的位置是不需要判断的, 因为除了溢出异常之外, 先导1的位置一定是第一个非符号数。

通过研究浮点数减法运算的几种情况, 可以得到前导1位置与操作数前三位取值的关系对应表, 如表1所示。在表中, A和B是不考虑符号位的两个操作数, 且均为补码形式, 因此对减法运算所做的研究都是基于补码的加法运算来进行的。

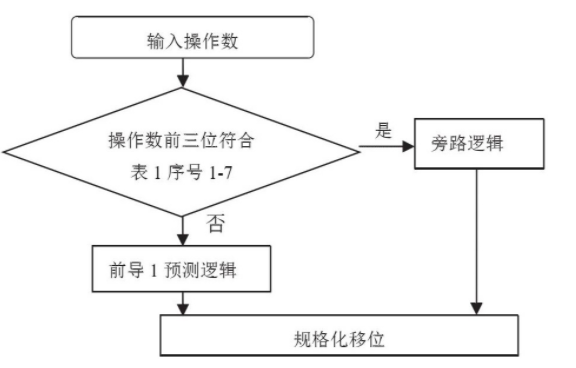

通过表1中对浮点运算的分析可以发现我们将浮点运算分成两个运算通道, 能够通过操作数的前三位确定前导1位置的操作数通过旁路逻辑, 而其他操作数通过传统前导1预判逻辑, 该算法如图1所示。

图1 双通道前导1预判模块的逻辑算法Fig.1 The algorithm of the leading-one prediction circuit by two path

2 双通道前导1预判模块的全定制版图设计

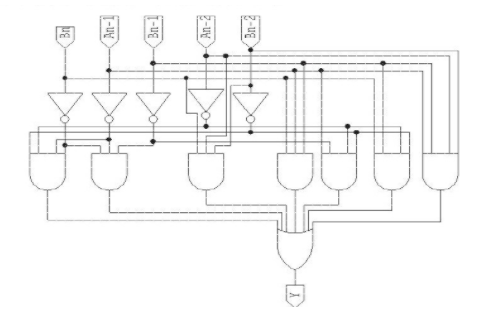

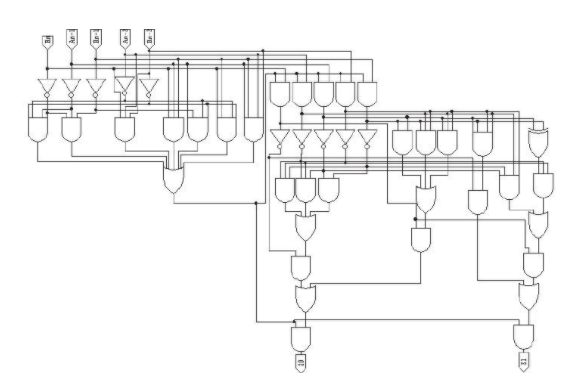

在双通道前导1预判模块中, 操作数判断逻辑的电路和旁路逻辑的电路如图2 (a) 和 (b) 所示[1].在图中可以发现反相器、4输入与门、3输入与门、2输入与门等门电路在电路结构图中多次被使用, 那在进行全定制版图设计的时候可以将这些单元做成基本单元, 调用时只需要按照需求调节其大小, 然后按照要求拼接出所需要的电路, 这样可以减少大量重复劳动, 提高画图的效率。

表1 前导1的位置与操作数前三位取值情况关系表Tab.1 The relationship between the position of the leading-one and the value of the first three bits of the operand

图2 (a) 操作数判断逻辑电路结构图Fig.2 (a) The circuit of the leading-one judgement circuit

图2 (b) 旁路逻辑电路结构图Fig.2 (b) The circuit of the bypass logic

用全定制方法进行版图设计的时候, 首先要确定单元的高度, 所有基本单元具有同样的高度, 这样便于拼接, 另外还好确定金属线的走向和分布, 如在图3的3输入与门中, 所有的金属2都是纵向走线, 且按照设计规则的要求进行间隔, 在需要用到金属2的时候, 只要找附近的金属2进行连接, 其余没有用到的金属2可以删除, 这样可以保证布线间距满足设计规则的要求且具有最高的利用率。由于在进行版图拼接的时候阱接触和衬底接触不能重叠, 所以在进行单元设计的时候要考虑到拼接后的位置关系, 为相邻的单元的阱接触和衬底接触预留出位置, 如图3所示。

图3 3输入与门版图实现Fig.3 The layout of the 3 inputs nand gate

单元版图设计完成后可以按照电路结构图拼接版图, 如图4所示, 在拼接的时候要考虑到布局的"艺术性", 版图设计不仅是一项技术, 同时也是一门艺术, 好的布局和布线能够给人以美感, 当然这要在保证布局的合理性和布线尽可能短的前提下完成的。

图4 拼接好的操作数判断逻辑电路的版图Fig.4 The layout of leading-one judgement circuit

3 版图的验证

版图布局和连线完成后还要进行设计规则检查 (DRC) 和电路图与版图对比验证 (LVS) , 在进行设计的时候, 首先要保证单元版图通过这两项验证, 然后才能进行拼接, 拼接后的版图要再进行一次DRC和LVS检查, 如果发现错误, 基本可以确定是在进行拼接和连线的时候出现问题, 而单元内部没有问题, 这种分层设计便于查找错误。

4 结束语

本文对双通道前导1预判电路的版图全定制设计方法进行了研究, 利用全定制的版图设计能够减少版图的面积, 进一步提高电路模块的性能。

参考文献

[1]王颖。改进溢出判断电路的设计与仿真研究[J].电子技术应用。2012.05:49-51.WANG Ying.Research on design and simulation of an improved overflow judgment circuit[J].Application of Electronic Technique 2012.05:49-51 (in Chinese)

[2]Behrooz Parhami.computer Arithmetic-Algorithms and Hardware Designs[M].Oxford University Press, 2000

[3]李笑盈。浮点加法运算器前导1预判电路的实现[J].计算机工程与应用。2002, 21:142-143LI Xiaoying.The Design of Leading-One Prediction in Floating-Point Adder[J].Computer Engineering and Applications.2002, 21:142-143 (in Chinese)