摘要:在超深亚微米工艺中, 数字集成电路版图设计由以前简单的物理验证进入到复杂的版图验证阶段。版图验证包含时序验证、形式验证和物理验证。时序验证进行电压降分析和时序分析, 确保时序收敛;形式验证进行两个网表的逻辑等效检查;物理验证进行可制造性、可靠性和设计规则检查, 确保版图符合可制造性工艺规则和电路规则。三种验证技术共同指导并约束着数字集成电路的物理实现, 灵活配置相关版图验证技术可进一步加快版图验证的进度。

关键词:超深亚微米; 版图验证; 时序验证; 形式验证;

Abstract:The layout design technology in SDSM digital ICs has evolved from simple physical verification to complicated layout verification. Layout verification consists of timing verification, formal verification and physical verification. The timing verification performs IR Drop analysis and timing analysis and ensures clock convergence. The formality verification performs equivalence checking of two net-lists. The physical verification performs DFM, reliability and design rule check and ensures that the layout complies with DFM rule and electric circuit rule. The verification technologies jointly guide and control the physical realization of digital ICs. Flexibly selection and collocation of layout verification technologies improve layout verification efficiency.

Keyword:SDSM (super deep sub-mircon) ; layout verification; timing analysis; formality verification;

1 引言

随着半导体工业进入到超深亚微米时代, 工艺越来越复杂, 数字集成电路设计规模越来越大, 导致在版图设计过程中未知的、不可控的因素逐渐增多, 遇到了大量的时序、信号完整性、可制造性和可靠性等方面的问题, 必须要做大量的版图验证工作来确保版图综合设计的正确性[1].版图验证工作已经占据整个设计周期的大量时间, 验证工作逐渐成为制约产品快速上市的瓶颈。因此, 在超深亚微米工艺中, 版图设计由以前的重版图综合设计阶段进入到重版图验证阶段, 由简单的物理验证进入到复杂的物理验证阶段, 研究版图验证技术显得十分重要[2].

2 版图设计流程

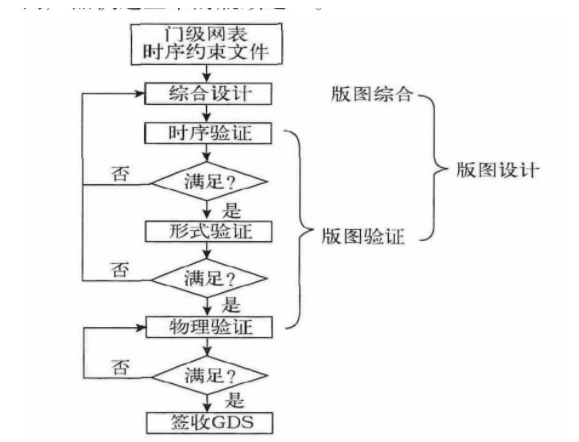

数字集成电路版图设计包括版图综合和版图验证, 图1为数字集成电路版图设计的典型流程, 版图综合设计利用EDA软件如Synopsys的ICC (IC compile) 综合软件进行, 先读入前端提供的门级网表和时序约束文件, 之后进行布局、时钟树、布线等设计就可以完成版图综合设计。版图验证包含时序验证、形式验证和物理验证, 通过对版图进行时序验证、形式验证来确保版图综合设计的正确性, 如果不满足要求就需要重新进行版图综合设计再来进行验证, 往往需要多次反复, 直至满足约束条件为止, 之后在Cadence的Virtuoso版图编辑软件上对全芯片版图 (包含IO) 采用Calibre软件进行物理验证, 如可制造性、可靠性、DRC、LVS等检查, 确保版图符合可制造、可靠性和电路等规则。芯片在全部通过版图验证后才能输出GDS数据进行制版流片[3].在超深亚微米工艺中, 版图验证时间和复杂度大幅度增加, 逐渐成为制约产品快速上市的瓶颈之一。

图1 典型数字集成电路版图设计流程

3 时序验证

时钟信号是数字集成电路中数据传输的基准, 它对于同步数字系统的功能、性能和稳定性起决定性作用, 因此, 在版图综合设计过程中, 时序验证是最重要的工作, 贯穿到布局、时钟树综合、布线等过程;时序验证分析可能影响时序不收敛的因素如电压降、时钟树等, 确保时序收敛。

3.1 电压降分析

电压降 (IR Drop) 分析可以用来衡量电源供电设计的好坏。由于芯片内部供电网络中寄生参数 (电阻、电容、电感) 的存在, 导致电源从Power PAD接口到达芯片内部各点的电势不同, 其差值称为电压降。过大的电压降会引起时钟的偏差增大和时序违例。一般5%的电压降会增大10%~15%的线延迟, 延迟值的增加会造成时序违例, 引起setup和hold违例, 导致芯片主频的降低, 甚至产生功能失效。

当对电源布局和布线设计完成之后, 就必须对电压降进行分析。使设计的电源布局符合电源预算规划, 更重要的是要保证不会对时序产生违例影响。

图2 电压降分析设置及芯片电压降分析示意

采用IC Compiler设计软件中的analyze rail选项可以很方便地进行电压降分析, 如图2中左边是电压降分析的设置界面, 选择Voltage drop analysis选项, 设置电源节点等参数, 电压降分析的结果如右边所示, 它可以通过一定的颜色层次形象地表达, 越往芯片中心的IR drop越大, 最大的结果必须小于设计要求值。如不满足要求, 可通过增加供电电源数目、增大供电网络宽度、增加供电网络密度等措施进行改善。

3.2 时序分析

时序分析 (Timing Analysis) 贯穿于设计过程的各个阶段:从RTL逻辑综合到版图布局、时钟树综合、布线等, 每一次分析的目的都是为了检查当前的设计结果是否满足设计的约束条件, 包括静态时序分析STA (Static Timing Analysis) 和动态时序分析DTA (Dynamic Timing Analysis) .

静态时序分析 (STA) 根据设计规范的要求通过检查所有可能路径的时序, 不需要通过仿真或测试向量就可以有效覆盖门级网表中的每一条路径, 在同步电路设计中快速找出时序上的异常。静态时序分析可识别的时序故障包括:建立/保持和恢复/移除检查 (包括反向建立/保持) 、最小和最大跳变、时钟脉冲宽度和时钟畸变、门级时钟的瞬时脉冲检测、总线竞争与总线悬浮错误、不受约束的逻辑通道, 还能计算经过导通晶体管、传输门和双向锁存的延迟, 并能自动对关键路径、约束性冲突、异步时钟域和某些瓶颈逻辑进行识别与分类。

动态时序分析主要指的是门级 (或对版图参数提取结果) 仿真。这种方法主要应用在异步逻辑、多周期路径、错误路径的验证中。随着设计向130 nm以下的工艺发展, 只用静态分析工具将无法精确验证串扰等动态效应。通过动态时序分析与静态时序分析相结合可以验证时序逻辑的建立-保持时间, 并利用动态技术来解决串扰效应、动态模拟时钟网络。

4 形式验证

在版图综合设计完成满足时序约束条件后, 进行形式验证。从RTL网表到门级网表, 不仅在逻辑综合阶段, 设计优化过程会对网表做出更新, 在物理设计阶段门级网表也是处于不断优化的过程当中, 在扫描链插入、时钟树综合、优化、人工网表编辑等之后, 在流程的每一阶段都能在门级维持完整的功能等效, 因此, 形式验证变得相当重要。

4.1 形式验证

形式验证 (Formality Verification) 是一种等效性检测工具, 用来判断一个设计的两个版本在功能上是否等效。主要包括两部分:一是等价性检查 (equivalence checking) , 二是模型检查 (model checking) .等价性检查主要是检查两个门级网表 (gate-level netlist) 之间是否一致, 保证网表处理后不会改变电路的功能, 保证网表能正确地实现RTL代码所描述的功能。这种方法主要是用来寻找实现 (implementation) 中的缺陷, 而不是设计中的缺陷。模型检查主要是检查RTL代码是否满足规范中规定的一些特性 (properties) .在规定这些特性时一般使用特性规范语言 (Properties Specification Languages) , 有的也使用基于断言的验证语言。由于这种方法可以在不需要仿真的前提下检查设计中所有可能出现的情况是否满足规定的特性, 所以使用这种方法不会遗漏任何的边界情况 (corner-case) .

4.2 ECO验证

由于物理设计周期很长, 当发现设计问题, 如果RTL网表和门级网表改变较小, 在设计的后期阶段, 可以通过工程改变命令 (ECO, engineering change order) 的方法对布局和布线做局部更新, 采用递增式的ECO, 添加新的逻辑门, 改变相应的连线, 还可以手动修改错误的逻辑信号之间的连线, 以达到快速通过验证的目的。

5 物理验证

物理验证除了传统的设计规则检查外, 对于超深亚微米工艺, 由于芯片特征尺寸不到光源波长的四分之一, 造成图形在转移、光刻中由于光学邻近效应的影响出现比较大的偏差, 需要进行可制造性设计来提高芯片良率。同时随着芯片功能的不断增多, 芯片采用更低的电压、功耗, 对时钟频率和电源、信号完整性等有更多的要求, 需要采用可靠性设计来提高芯片的可靠性。因此物理验证包含的内容很多, 对可制造性、可靠性检查也越来越重视, 一般采用Calibre软件进行可制造性、可靠性和设计规则检查, 确保版图符合可制造、可靠性和电路等规则。

5.1 可制造性检查

可制造性检查 (design for manufacturing, DFM) 包含版图适印性验证、天线效应检查、金属密度检查等。在超深亚微米工艺中, 图形生成几乎是在分辨率极限下进行的, 而晶体管数量则以指数增长。当光刻图形生成被推向极限时, 仅一个单一的缺陷就可能导致一片含有数百万个晶体管的芯片失效, 为保证图形从版图到工艺加工的有效转移, 提高版图适印性, 控制参数偏差以实现芯片制造的可重复性、高成品率以及高成本效益, 因此可制造性检查十分重要。

5.1.1 版图适印性验证

版图适印性验证 (layout printability verification, LPV) 用于对光学邻近效应修正的版图进行全芯片工艺仿真, 旨在解决版图的适印性问题。进入超深亚微米工艺以后, 集成电路的特征尺寸接近曝光系统的理论分辨率极限, 光刻后硅圆片表面成像产生明显的畸变, 导致光刻图形质量的严重下降, 导致设计线宽与最终转印的线宽之间出现偏差。因此, 版图适印性验证采用分辨率增强技术, 考虑图形邻近效应会造成的失真, 对版图设计图形进行修改, 达到提高图形转移质量的目的, 满足可制造性设计规则, 减小器件和互连线的参数偏差。

5.1.2 天线效应检查

天线效应 (antenna effect) 由版图结构引起, 在CMOS制造的中间步骤引起成品率和可靠性的问题。在深亚微米工艺制作中, 当金属互联线上的静态电荷过量积累和放电, 使得有电流通过CMOS的栅极时, 相对于栅极的面积, 如果与栅极直接相连的或者通过下一层连接到栅极的电容面积比率很大时, 放电可以影响到栅氧化层的性能, 有可能损坏、严重时使芯片失效, 这种现象称为"天线效应".在版图综合设计布线过程中, 调用天线规则进行布线, 一般采用改变布线顺序、插入天线二极管和插入跳线等方法, 使版图布线满足天线要求, 综合设计完成后, 进行天线效应检查, 再次确认版图布线符合天线规则要求。

5.2 可靠性检查

特征尺寸的缩小以及制造过程中的偏差引起了越来越多的可靠性问题, 如电路功耗、电流密度、ESD等, 通过可靠性检查排除不良设计对电路的影响, 确保设计满足可靠性准则要求。

5.2.1 功耗分析

电路功耗决定了芯片的工作温度和电路的可靠性, 因此功耗分析就成了不可缺少的重要步骤, 版图设计时主要进行动态功耗分析, 分析结果体现了芯片的能耗大小、芯片内部电压降和电流的分布, 也反映了芯片工作稳定的程度, 因此我们需要将芯片的功耗、压降、电迁移等参数控制在合适的范围内。电源网络设计为芯片的供电提供可靠的保障, 而功耗分析对其规划方案的最终结果进行检查及分析。功耗分析的结果不仅要符合电源预算规划, 而且要保证不会对时序产生违例影响。

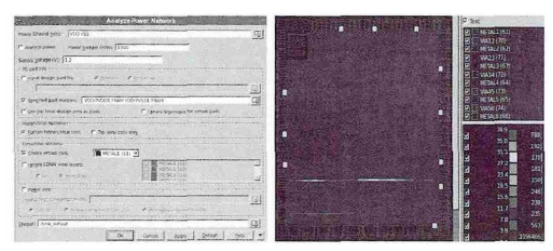

采用IC Compiler设计软件中的Analyze Power Network选项进行功耗分析, 如图3中, 左边是功耗分析的设置界面, 可设置需要分析的电源节点、电源电压、功耗大小等, 功耗分析的结果如右边所示, 可以通过不同的颜色层次而形象地表达功耗大小, 如不满足要求, 可通过分散布局功耗较大的物理单元、降低物理单元传输时间、采用漏电小的标准单元等措施进行改善。

图3 功耗分析设置及芯片功耗分析示意图

5.2.2 电迁移分析

电迁移是由于过大的电流使金属线断裂引起电路失效的现象, 对于作为互连线的金属层来说, 所能允许流过的最大电流是有一定限度的。在纳米工艺下, 随着线条越来越细, 更容易受到电迁移的影响, 电迁移分析的目的是使芯片不因过大的电流使金属连线断裂, 导致芯片失效。采用IC Compiler设计软件中的analyze rail选项进行电迁移分析, 图2中可进行电迁移分析的设置, 选择Electromigration analysis选项, 设置电源节点等参数, 分析结果如不满足要求, 可通过增加电源金属线宽、增加电源条线、采用承受电流密度更大的厚层金属进行电源网络设计等措施改善。

5.3 设计规则检查

设计规则检查包括几何设计规则检查 (DRC, design rule check) 与电路版图一致性规则检查 (LVS, layout versus schematic) , 是基础的检查, 通过规则检查是版图设计的最低要求, 是版图流片成功的重要保障。

5.3.1 几何设计规则检查

几何设计规则检查的主要目的是检查版图中各掩模相关层上图形的各种尺寸, 保证无一违反设计规则。晶圆代工厂对各自不同工艺参数制定出满足芯片制造良率的同一工艺层及不同工艺层之间几何尺寸的最小值, 这些最小值规划的集合就是版图设计规则。在超大规模数字IC中, 在版图编辑的过程中很难避免设计错误, 因此首先检查芯片顶层的图层尺寸, 不检查标准单元, 减小检查版图数据, 加快检查速度, 当完成顶层检查后, 再进行最终包含标准单元的检查, 根据软件提示进行修改, 直至版图满足所有设计规则为止, 提高了芯片的验证速度。

5.3.2 电路版图一致性规则检查

电路版图一致性规则检查是把从版图所提取的电路网表与原设计的电路网表进行比对, 检查两者在结构上是否一致, 检查内容主要包含连接关系和器件类型尺寸是否一致。检查过程利用EDA工具, 首先根据LVS提取规则, 从版图中抽取出版图所确定的网表文件, 然后将抽取出的网表文件与电路网表文件进行比较, 如果两个网表的电路连接关系和器件完全一致则通过LVS检查。反之, 说明版图存在与电路不一致的地方, 需要进行检查并加以处理或修改更正。对于超大规模数字IC芯片设计时, 采用分层次的检查方法, 即在底层完成标准单元和模块的LVS检查, 最后回到设计的顶层, 对顶层设计进行检查, 缩短了芯片的LVS检查时间。

6 结论

在基于0.13μm的某低功耗So C芯片设计中, 电路工作电压1.2 V, 频率250 MHz, 电路功耗要求小于30 m W, 电压降要求小于60 m V.针对电路低压低功耗高频的特点, 在时序验证时重点对电压降进行分析, 通过增加供电电源数目、增大供电网络宽度、增加供电网络密度等措施降低电压降, 同时对高频时钟进行完整性检查, 降低串扰, 并在布线时考虑可制造性设计规则, 采用递增式的ECO, 添加新的逻辑门和改变相应的连线, 进行快速验证;在功耗分析时通过分散布局功耗较大的物理单元、降低物理单元传输时间、采用漏电小的标准单元等措施进行改善;在LVS验证时采用分层次的检查方法, 即在底层完成标准单元和模块的LVS检查, 最后回到设计的顶层, 对顶层设计进行检查, 缩短了芯片的LVS检查时间, 从而大大缩短了版图验证时间, 提高了设计效率。最终芯片版图见图4, 面积2.5 mm×2.2 mm, 通过了后仿真, 仿真结果满足了设计要求。

图4 某So C芯片版图

总之, 超深亚微米工艺后, 版图设计由以前的重版图综合设计阶段进入到重版图验证阶段, 由简单的物理验证进入到复杂的物理验证阶段。时序验证、形式验证和物理验证看似三类不同性质的工作, 但它们紧密相关, 互为依赖, 共同约束着数字集成电路的物理实现。一般基于超深亚微米数字集成电路版图设计都应该进行上述三种验证工作, 但有些可根据设计的难易程度以及设计经验进行简单的时序验证、物理验证, 或者省略其中的某些验证, 如在0.18μm及以上工艺, 噪声问题不明显, 且当芯片的主频不高时, 可以不进行信号完整性时序检查;在0.13μm及以上工艺条件下, 不用多模式多端角做时序检查;而当设计不关心功耗、并对自己的电源网络设计有着十足的信心时, 也可以不进行功耗分析。可以说版图验证工作越来越复杂, 越来越具有挑战性, 如何灵活配置相关版图验证技术、加快版图验证的进度同样值得我们去研究。

参考文献

[1] 王仁平, 何明华, 魏榕山。基于MCU的So C芯片版图与验证[J].福州大学学报 (自然科学版) , 2011, 8.

[2]陈春章, 艾霞, 王国雄。数字集成电路物理设计[M].北京:科学出版社, 2008.

[3]Sandip Kundu, Aswin Sreedhar.纳米级CMOS超大规模集成电路可制造性设计[M].王昱阳, 谢文遨, 译。北京:科学出版社, 2014.