摘要:提出了一种具有开放式架构的新型高速数据传输终端平台,它以RapidIO作为各处理板卡的监控指令接口,以两个8×PCIe作为各处理板卡的数据接口。设计了有源交换网络背板实现系统互联;设计了通用处理板卡通过软件重构以实现数据上行调制或数据下行接收功能;下行接收的数据通过块数据传输,传输速率最高达40 Gb/s;通过独立磁盘冗余阵列扩展固态盘阵列实现数据高速记录,数据记录速率不低于500 MB/s;通过万兆以太网接口实现数据高速实时转发,数据转发速率不低于4 Gb/s;上行调制数据实时注入实时调制,数据速率不低于2 Gb/s.该平台硬件可扩展,软件可升级,控制和数据总线解耦合,可通过软件重构实现功能配置和在线更新,具有良好的扩展性和通用性,已在地面终端站高速数据传输系统中得到工程应用。

关键词:卫星地面站; 高速数据传输终端; 软件重构; 开放式架构;

Abstract:A new high speed data transceiver platform with open architecture is provided in which serial RapidIO is performed as control and command interface and PCIe with two 8 lanes is performed as data interface.Data exchange is realized through active switching network backplane.The common processing board is designed to realize modulation or data receiving function by software reconstruction.The data received in the downlink can be transmitted through block data with transmission rate up to 40 Gb/s.High-speed data recording can be realized through redundant array independent disk(RAID) extended solid-state disk(SSD) array with data recording rate to 500 MB/s.Data can also be transmitted through 10 GbE(Gigabit Ethernet) interface with data rate to 4 Gb/s.Modulation data is injected and modulated in real-time with rate to 2 Gb/s.The platform can be expanded in hardware,upgraded in software,decoupled in control and data bus,and function programme and online update can be realized through software reconfiguration.It has good scalability and versatility.It has been successfully applied in ground terminal station high speed data transmission system.

Keyword:satellite ground station; high speed data transceiver; software reconfiguration; open architecture;

0 引 言

近年来,随着高速无线通信应用领域的不断拓展,特别是在侦察、中继、资源探测、高分辨率对地观测等卫星中,高速数据无线传输技术应用已越来越广泛。而作为高速数据无线传输系统中的地面终端设备需要对接的卫星种类越来越多,支持数据调制解调方式多种多样,数据传输带宽越来越宽,编译码种类越来越多,这也成为今后高速数据传输终端必然面对的工程需求。

传统高速数据传输终端的整机架构有以下几种方式:一是采用商用的外围组件互联(Peripheral Component Interconnect,PCI)或外围扩展组件互联(Peripheral Component Interconnect Express,PCIe)整机,在具有PCI[1]或PCIe[2]接口的服务器主板基础上设计功能卡,每个卡完成一部分独立功能[3],如法国In-snec公司提供的相关产品便是此种架构。这种架构的优点是主板为标准商用产品,设计只需重点关注PCI/PCIe功能卡的设计;缺点是功能卡没有扩展能力,每一个功能卡和其他功能卡之间的通信要么通过板卡间的高速飞线解决,要么通过PCI或PCIe总线进行,给CPU添加了额外的负担。二是采用紧凑外围组件互联(Compact Peripheral Component Interconnect,CPCI)或VPX架构工控机,在其上定制开发功能板卡,如国内一些高校和科研院所提供的相关产品采用了此架构。CPCI或VPX为标准架构,也有足够多的自定义管脚。CPCI具有低成本特点[4,5],但它没有高速传输链路,难以满足传输数据量大的场合;VPX具有丰富的高速传输链路[6],但VPX机箱动辄上10万的售价也限制了其推广,且对于4U高度的上架设备,VPX只能提供6个槽位,除去系统主板和中频信道组件占据的槽位外,可自定义的槽位只有4个,若要使用更多的功能板卡需要增加机箱高度,不利于设备整体外观的设计和重量的控制。此外,随着高速星地通信速率的不断提升,在实际使用中发现高速块数据在通信过程中控制指令响应不及时的问题也越来越突出。

因此,本文针对传统终端具有的问题,设计出了一种具有开放式架构,硬件可扩展、软件可升级,控制和数据总线解耦合,且设备成本可控的新型高速数据传输终端平台。

1 系统架构方案

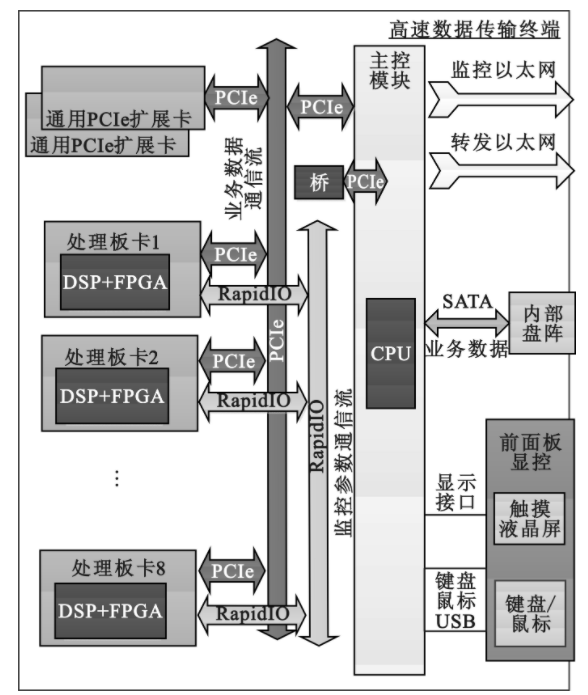

本文提出了一种具有开放式架构、支持板卡硬件和软件功能可重构、可升级、可扩展的高速数据传输终端平台,它具有PCIe和RapidIO高速双串行总线,将命令和状态信息通过4×高速串行RapidIO进行传输,并由各处理板卡上的数字处理器(Digital Signal Processer,DSP)来处理;将需要大数据量传输的块数据通过8×高速PCIe接口进行传输,并由各处理板卡上的可编程逻辑门阵列(Field Programmable Gate Array,FPGA)处理。通过此种方式实现了系统的控制命令和传输数据解耦合,降低了各芯片的处理压力,提高了系统实时响应能力和可靠性。

同时,该终端具有开放式特点。采用标准的信号定义,便于今后硬件板卡升级后可原位替代;软件上考虑到多种调制解调方式、多种编译码等的适配性,需FPGA、DSP软件可支持在线可重构,支持程序在线更新,以保证设备的可维护性和可升级能力,具有良好的扩展性。

高速数据传输终端平台设计的主要思想可概括为:数据总线和控制总线分离,以提高鲁棒性;尽量支持多的独立处理通道,以提高扩展性;尽量支持商用扩展卡,以降低成本。

根据以上设计思路,本文设计的终端系统总线采用了高速串行PCIe和RapidIO双串行总线,可根据用户需求配置多个处理单元,具有多个标准PCIe扩展槽位,可支持商用货架接口板卡。其中,RapidIO支持2.1规范,通信速率为4 lanes 3.125 Gb/s,最高支持6.25 Gb/s;PCIe遵循3.0规范,通信速率为8通道8 Gb/s,单个PCIe接口带宽可达40 Gb/s,可以满足常用处理板卡接口速率的带宽要求。

通用处理板卡通常采用DSP+FPGA的结构,使用DSP连接RapidIO接口作为板卡级监控管理处理芯片,使用FPGA连接PCIe接口用于大数据量的块数据的发送和接收。通用处理板卡通过软件重构可配置成为数据上行调制单元,也可以配置成为数据下行接收单元。其中,数据上行调制单元接收块数据用于数据注入并调制,数据下行接收单元将接收到的块数据组包后传给系统主板进行存储。通过监控接口可发送程序在线更新指令,对各板卡上各FPGA、DSP单元进行程序更新。另外,通过DSP和板上固件配合工作,可实现板卡的可重构,实现可升级。若终端设备后续需要硬件升级,可将符合规范定义的板卡插入预留的槽位,完成硬件的升级。

对于通用PCIe槽位,可扩展支持具有×8接口的标准商用的接口卡,如万兆以太网卡、独立磁盘冗余阵列(Redundant Array Independent Disk,RAID)控制卡、光纤扩展卡等,以实现对外接口的扩展。

对于4U 19吋(1吋=2.54厘米)标准上架结构的VPX工控机来说,由于结构尺寸限制,只能插入4张自定义板卡,而本文设计的处理终端有效利用了4U机架深度的空间,在4U高度中可插入2张通用PCIe扩展卡,8张通用处理板卡。此外,使用符合PICMG 1.3标准的工业单板计算机提供主控模块功能,可提供Windows或麒麟操作系统的人机交互界面。

高速数据传输终端系统架构方案框图如图1所示。

图1 高速数据传输终端系统架构框图

2 终端设计实现

2.1 终端有源交换网络实现

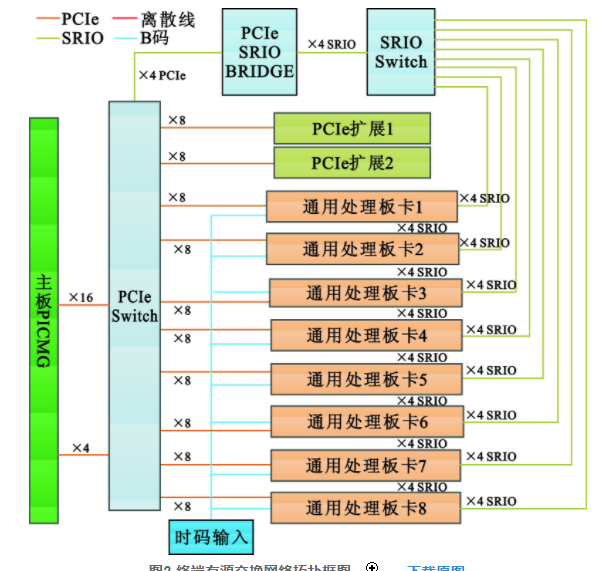

为了节省板卡空间,将更多的槽位留给处理板卡,区别于一般CPCI、VPX平台采用无源背板外加交换模块的方式,本文将终端的PCIe+RapidIO交换网络功能整合到有源背板上,既合理利用了背板空余空间,又为功能板卡留出了更多的自定义槽位。

主板选用基于PICMG 1.3规范的主板,它具有1个16×PCIe 3.0接口和1个4×PCIe 2.0接口。

在有源背板上设计PCIe交换芯片,扩展1路4×PCIe 2.0接口,再通过PCIe转RapidIO桥接芯片转换为4×5 Gb/s的RapidIO总线,其后再通过RapidIO交换芯片将RapidIO接口扩展为多个接口分别连接到各个板卡,从而实现终端控制总线的接口扩展;通过PCIe交换芯片的其他8×PCIe 3.0接口分别连接到所有8个通用数字槽位和2个标准PCIe扩展槽位,从而实现数据总线的接口扩展。

高速数据传输终端有源交换网络拓扑框图如图2所示。

图2 终端有源交换网络拓扑框图

2.2 下行通道数据接收实现

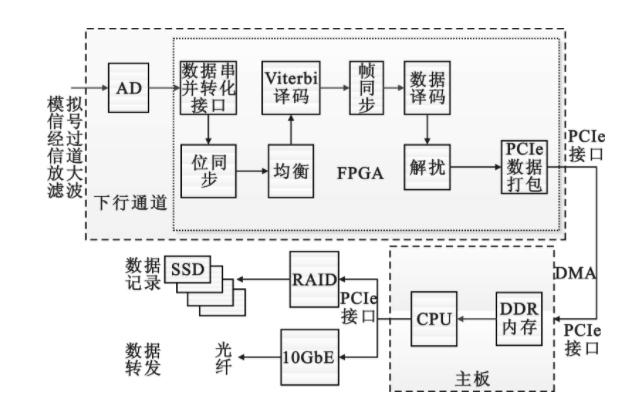

高速数据传输终端接收卫星传输下来的高速数据,通过解调、译码完成信道解码,本地暂存或者实时传输给用户实现后级信源解码、解密等。

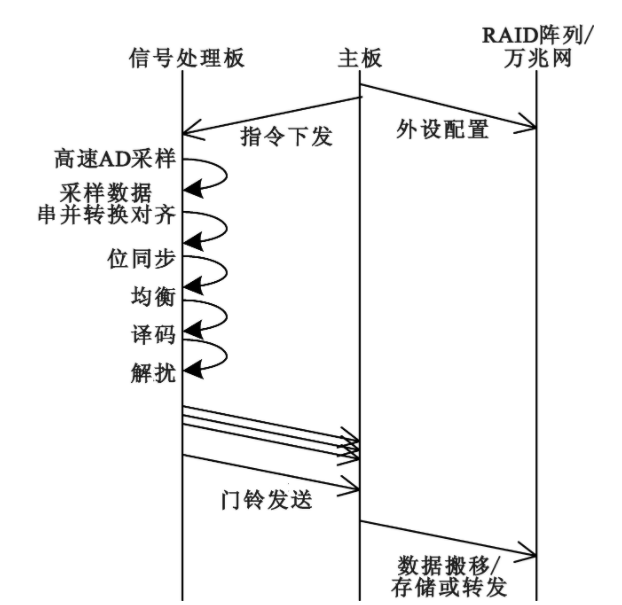

信号下行通道的具体实现步骤为:接收的卫星信号放大滤波后,通过高速模数转换器(Analog-to-Digital Converter,ADC)采集,在FPGA中实现数字下变频,位同步、均衡、解调,完成数据帧同步、译码、解扰;然后将数据通过PCIe接口以直接存储器访问(Direct Memory Access,DMA)方式存入到主板内存[7],并向中央处理器(Central Process Unit,CPU)发送门铃;CPU接收到门铃后从内存取数,将数据拷贝存入到终端外设RAID磁盘整列[8]或直接通过万兆以太网口转储到外部存储服务器。

下行通道数据解调、译码、记录、转发数据流框图如图3所示。

图3 下行通道数据流框图

终端在正常工作,通过数据实时记录或实施数据转发的设备状态运行流程图如图4所示。

图4 接收工作状态运行流程图

2.3 上行通道数据调制实现

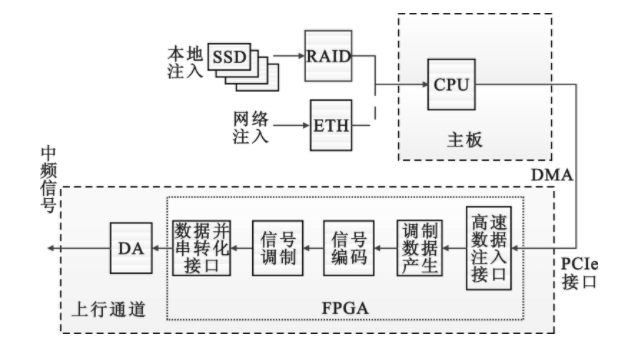

高速数据传输终端将用户数据通过信道编码、调制到中频,通过前端调制功放、调制,经天线系统上传到卫星。

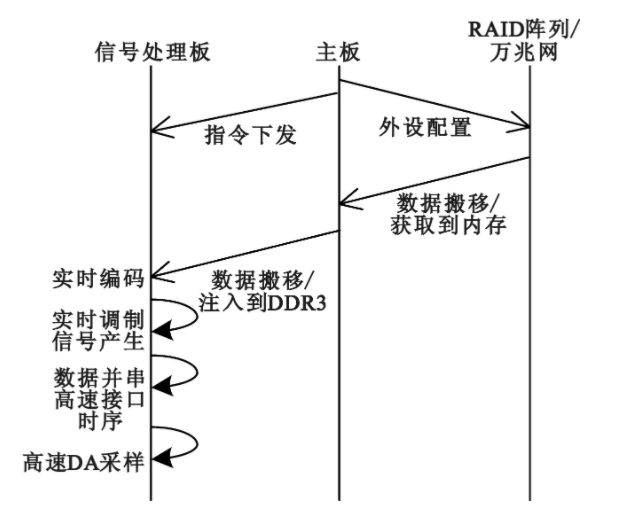

信号上行通道的具体实现步骤为:用户数据通过以太网或通过本地存储文件注入,通过PCIe接口的DMA方式注入到调制模块;FPGA将注入数据通过调制数据实时产生、编码和实时调制,同时配合高速数模转换器(Digital-to-Analog Converter,DAC)芯片直接生成编码调制后的中频模拟信号,再将信号送入后级信道变频放大发射,如图5所示。

图5 上行通道数据流图

终端在正常工作,调制数据注入后通过实施编码、调制、发射的设备状态运行流程图如图6所示。

图6 发射工作状态运行流程图

3 验证和测试

对本文提出的高速数据传输终端平台进行验证和测试的主要指标包括高速总线传输能力测试、数据记录能力测试、数据注入能力测试。

3.1 高速背板总线传输指标测试

使用WINNET公司PCIe专用测试仪iTL32403-LL对每个插槽的PCIe总线传输能力进行测试。在8×5 Gb/s的条件下,测试数据量为1013,测试时间大于30 min,各通道误码率均为0,证明单个模块通过高速背板PCIe总线传输能力可达40 Gb/s.

3.2 解调数据记录能力测试

本终端数据记录使用基于Windows文件系统的数据记录,使用SSD Benchmark工具对盘阵速率进行测试,在8盘RAID0条件下,磁盘阵列读写的速率均超过2 000 MB/s.

在实际工程中,由于数据存储是带文件系统的存储,会带来存储效率降低,按照工程要求,终端需接收双路2 Gb/s的解调数据,即4 Gb/s速率通过下行通道并实时记录解调数据,FPGA解调后的双通道数据通过PCIe DMA传给主板DDR3,再记录到SSD阵列,实时记录连续存储不丢包,证明数据存储能力不低于500 MB/s.

3.3 调制数据注入能力测试

本终端具有数据注入功能,将存储在SSD阵列上的调制数据通过PCIe总线注入到通用信号处理板上,可满足数据注入速率不低于1 GB/s的要求。

在实际工程应用中,实时调制数据传输带宽为2 Gb/s,FIFO流控工作正常,无数据丢失和溢出,证明数据实时注入、实时调制能力不低于2 Gb/s.

(4)数据转发能力测试

本终端具有数据转发能力,将存储在SSD阵列上的解调数据通过万兆以太网接口实时转发到外部设备。

在实际工程中,终端接收双路2 Gb/s的解调数据,即按照4 Gb/s速率通过下行通道实时解调数据,FPGA解调后的双通道数据通过PCIe DMA传给主板DDR3,再通过万兆以太网接口卡转发到外部万兆交换机,数据转发连续不丢包,证明数据实时转发速率不低于4 Gb/s.

4 结 论

与传统的高速无线传输终端相比,本文提出的基于开放式架构的高速数据传输终端平台具有低成本、多总线、通用性、大带宽、高密度等特点,具体表现在以下几方面:

(1)避免VPX等昂贵的设备架构,在普通工控机基础上改进得来,降低了成本。

(2)设计PCIe数据总线和RapidIO命令总线分离,降低各芯片负载压力,提高了系统鲁棒性。

(3)使用通用信号处理模块可实现任意功能在任意板卡上的动态配置和部署,板卡可重构、可在线升级,具有良好的扩展性。

(4)利用PCIe 3.0高速总线,板卡间数据传输带宽可达到40 Gb/s.

(5)数据记录、转发能力可达4 Gb/s,数据注入能力可达2 Gb/s.

(6)在4U工控机大小上实现1个主板、8个自定义板卡和2个标准PCIe卡,电路设计密度最大化,最大扩展了能力。

综上所述,基于开放式架构的高速数据传输终端平台作为地面收发终端,可满足星地间吉比特高速无线数据传输、记录、转发的需求,已在地面终端站高速数据传输系统中得到工程应用,在嵌入式高速无线宽带通信等领域具有推广意义。

参考文献

[1] 王海明,胡金龙,吴丽华。基于PCI总线的高速数据采集卡设计[J].计算机测量与控制,2012,20(12):3393-3396.

[2] 李木国,黄影,刘于之。基于PCIe总线的高速数据采集卡设计与实现[J].测控技术,2013,32(7):19-22.

[3] 李文磊。基于PCIE总线的高速数据传输系统的设计与实现[D].成都:电子科技大学,2016.

[4] 刘进军。采用CPCI总线的通用高速数传接收机[J].电讯技术,2012,52(10):1644-1647.

[5] 钟瑜,刘红伟。KSA高速卫星基带数据实时处理架构设计与实现[J].电讯技术,2019,59(6):659-666.

[6] 宋玉霞,李贵,甘峰,等。基于TMS320C667x和VPX的雷达处理系统设计及应用[J].无线电工程,2016,46(11):71-74.

[7] 李超,邱柯妮,张伟功,等。基于PCIE总线主模式DMA高速数据传输系统设计[J].电子技术应用,2015,41(9):142-145.

[8] WANG S M.PCIE interface design for high-speed image storage system based on SSD[C]//Proceedings of 2014 International Symposium on High Power Laser Systems and Applications.Chengdu:SPIE,2015:135-141.

随着动画产业的兴起,我国各高校都业已开设了动画专业。但目前的基础课教学严重制约了动画教学。原因一,在课程的设置上,基础课课时少,绝大多数院校在大一就基本完成了所有基础课教学。...

我国存在视力障碍的人数位列世界前茅,政府关爱视力障碍人群,设置了全世界长度最长、分布最广的盲道,但日常生活中我们却很少看到他们走在盲道上。...