0 引 言

随着航天科技、电子技术的不断进步,以及空间探测任务需求的不断提升,基于各种应用的航天器设备的复杂度和数据量也显着增大,设备在不同任务阶段产生各种发生率、数据格式及通信接口标准的数据源包,且关联设备间数据共享需求增多。为适应空间应用系统数据业务标准化、系统化的发展方向,以及多设备协同工作需求,需为多设备提供灵活高速的数据管理业务。

传统航天数据业务中各载荷设备通过多路数据传输总线或专用高速串行数据总线直接与上级分系统互连,限制了载荷设备数量及支持的数据格式。同时,传统航天器设备功能比较简单,设备间独立工作,而随着航天器任务的不断发展,同一应用过程可由不同设备完成,一个设备也可包含多种应用过程,在这些关联设备间进行灵活数据交换是实现多设备协同工作的有效途径。文中提出了一种面向空间数据系统的多设备数据管理方式,适用于设备复杂的有效载荷或其他关联过程设备管理需求。低速数据通道控制设备工作程序并监测工作状态。对复杂的业务数据采用基于应用过程的分区管理、存储转发方式,响应上层分系统指令,动态调度各类数据经由高速数据通道在需求设备间交换。扩展分系统可管理设备数量及支持的数据格式,实现设备间业务数据共享。

1 系统分析

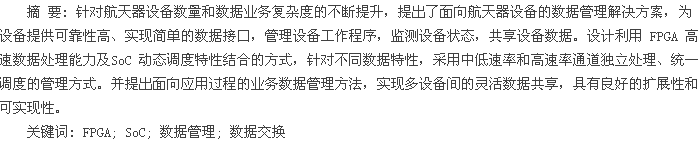

目前在航天器数据系统中普遍采用 MIT-STD-1553B 总线标准,并通过高速串行数据总线作为高速数据专用通道。因此,设备数据管理单元功能包括:

( 1) 接收上级分系统转发的开关命令和数据注入,解析后通过低速串行总线接口通知对应设备;( 2) 采集设备状态数据,并通过 MIT-STD-1553B上传至分系统;( 3) 接收设备不同任务及状态下产生的业务数据,按数据注入调度要求将数据在设备间共享或上传至分系统。

图 1 中设备数据管理单元管理的数据类型及数据特性为:

( 1) 开关命令和数据注入,为随时产生的数据包,数据量小,需实时响应该数据。

( 2) 状态数据,包括设备健康数据、工作状态数据等,需实时监测,数据量小,数据管理单元周期性采集各设备状态数据,格式化后上传至分系统。

( 3) 业务数据,该部分数据类型及流向复杂,包括图像、话音等信息,不同设备产生各种发生率、数据长度的数据源包,这些数据源包可属于一个或多个数据过程。数据管理单元根据应用过程动态组织业务数据在不同传输格式的设备中共享,并将其封装后经高速串行数据总线传输至分系统。

设备数据管理单元为多设备提供可靠、实现简单的数据接口方式。解析开关命令和数据注入管理设备工作程序,支持设备自定义的业务数据格式,多路后转发至上层分系统,并在各设备间实现基于应用过程的数据交换。

2 系统实现

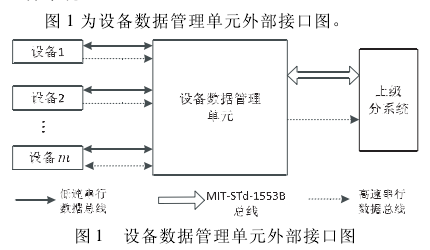

( 1) 硬软件协同设计

由于业务数据量大、传输速率高以及空间环境的特殊要求,采用专用集成电路的软硬件协同优化设计方法是实现高速、高可靠数据系统的主要途径,特别是集成了处理器、存储器、逻辑器等多种硬软 IP 核的平台级 FPGA。文中基于内嵌处理器 PowerPC 的 FPGA设计多设备数据管理的实现方案。考虑软件调度的灵活性及 FPGA 的高速处理能力划分数据管理单元组成如图 2。

如图 2 所示,利用 SoC 的灵活性管理设备执行开关命令和数据注入并采集设备健康数据,而对于数据量大、数据速率高的业务数据则利用 FPGA 的高速及并行处理能力完成数据存储和封装,SoC 在这一过程中仅负责路径管理调度,确保了不同类型数据的并行处理和灵活交互。

( 2) 开关命令、数据注入及状态数据管理

根据系统分析,分系统通过开关命令及数据注入控制设备工作并提供环境参数,同时定期采集状态数据监测设备工作状态。设备数据管理单元实时响应分系统发送的开关命令和数据注入,并在上电状态下周期性监测各设备状态。其数据长度,封装格式和数据发生率都与业务数据存在较大差异,因此采用专用低速信道处理该类数据。在工程实现过程中,由 FPGA 负责外部设备与嵌入式处理器接口协议转换,嵌入式处理器响应并解析上级分系统的开关命令和数据注入,解析后按事件有效时间通知相关设备执行对应功能。同时,在每一状态数据采集周期,通过低速总线依次采集各设备状态数据,打包成设备状态数据源包,转发到上级分系统。

( 3) 业务数据管理

对于设备在任务不同阶段产生的多种业务数据,由于其突发性强、数据速率快、数据流向复杂,利用FPGA 并行处理能力实现对各通道业务数据的接收、处理、缓存及发送,并由 SoC 完成多路转发路径管理。

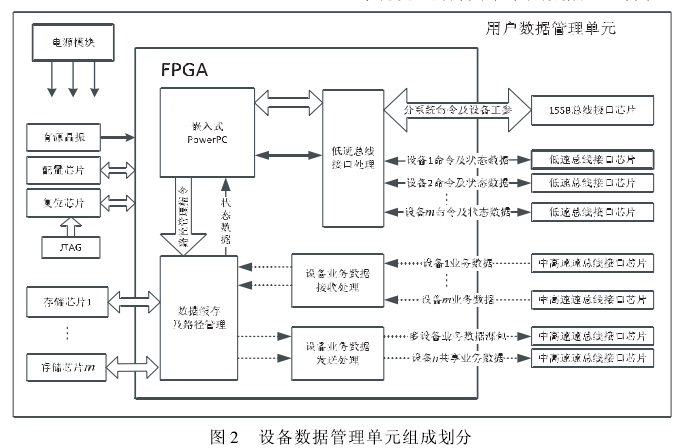

图 3 为业务数据管理设计框图

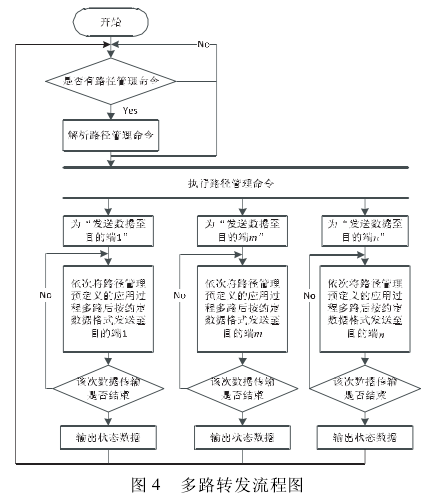

业务数据管理功能在接收端支持多信道数据同时处理,依据设备数据帧格式提供解码、有效性检查、数据包封装等功能。处理后的数据缓存在各通道 FIFO中,由数据缓存及路径管理功能依次写入缓存芯片。数据缓存及路径管理模块是业务数据管理的核心,提供数据的合路存储及多路转发功能。模块对接收端各通道 FIFO 内的缓存数据进行轮询读取,读缓存数据阈值可设置。读取后的数据按不同应用过程分区存入缓存芯片不同地址段。在转发数据的过程中,考虑空间任务各应用过程的执行流程和功能的确定性强。因此,在路径管理的实现上可采用固定路径的数据传输方式,即预先定义需传输至上级分系统及各设备的应用过程。在接到对应的转发命令后,依次从缓存区中读取对应应用过程数据,发送至各目的端通道数据缓存 FIFO,写缓存数据阈值可设置。图 4 为响应路径管理命令完成多路转发的流程图。业务数据发送管理功能提供数据帧封装及传输速率控制,将缓存区中的共享数据按目的端设备支持的数据格式封装,并依设备端数据处理能力控制数据传输帧间隔,各通道发送数据处理过程独立。

3 系统数据处理能力分析

针对文中提出的航天器设备的数据管理实现方法,分析系统可管理的设备数量、可处理的峰值速率与系统资源的关系。系统对开关命令、数据注入及设备数据的执行与采集采用 SoC 多线程调度处理方式,且需处理的数据量小,因此可有效管理该类数据。对于大数据量的业务数据,系统采用并行处理方式管理,其处理能力受FPGA 片上资源、存储芯片容量和读写速度影响。其中 FPGA 片上资源限制 SoC 缓存区大小、缓存FIFO 数量、缓存阈值、数据帧编 / 解码复杂度以及单通道可支持的串行数据速率。存储芯片容量决定系统可缓存转发的数据容限,读写速度则限制系统输入输出峰值速率。

随着微电子工业的发展,FPGA 的规模越来越大,集成度可达上千万门,系统工作时钟达数百 MHz,在系统方案论证阶段通过分析系统数据处理任务选择适合的 FPGA 型号可满足当前航天器设备数据管理业务需求。对于业务数据的存储转发功能而言,存储芯片按设备覆盖的应用过程划分成独立存储空间,划分后的空间大小决定该应用过程可一次存储转发的数据量( 缓存数据被转发到各约定目的端后数据可覆盖) 。

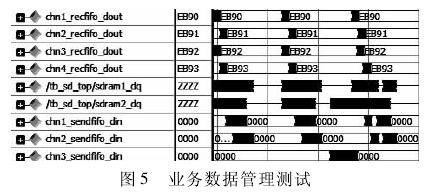

存储芯片的读写速度决定系统可实时处理的最高峰值速率。由于许多存储芯片如 SDRAM、NANDFLASH等都支持突发式存储方式,以一个 16 位宽,工作时钟80 MHz 的存储芯片为例,其在输入输出端可同时收发的峰值速率大于1 Gbps。在实际工程实现中还可通过存储芯片并联或多个芯片分布处理不同信道等方法进一步提高系统可支持的峰值速率。4 系统验证。为了验证系统功能,搭建测试环境,包括分系统开关命令、数据注入和设备状态参数模拟源、业务数据模拟源、以及存储芯片仿真模型。经测试验证,文中设计的设备数据管理单元能顺利解析并处理分系统开关命令和数据注入,正确采集设备状态数据,同时实现多数据通道基于应用过程的多路存储转发功能,转发时间可由路径管理命令动态控制。

图 5 为 4 输入及 3 路输出通道业务数据管理测试情况,存储芯片选取两片 16 位宽 SDRAM 分布存储,接收端各通道数据实时接收处理,发送端在接到路径管理命令后,按路径管理预定义的应用过程数据类别转发数据。

5 结束语

文中分析了航天器设备数据管理在空间数据系统发展中的重要作用,并提出基于平台级 FPGA 的实现方法,适应航天器设备不断增多、复杂度不断提升的发展方向。采用低速率和高速率信道并行处理、统一调度的策略管理各设备数据。经测试验证,可保证开关命令、数据注入及设备状态数据处理的实时性,业务数据高速转发,数据格式及交换路径灵活,有广阔的应用前景和实用价值。

参考文献:

[1] 谭维炽,顾莹琦. 空间数据系统[M]. 北京: 中国科学出版社,2004.

[2] 孙辉先,陈小敏,白云飞,等. CCSDS 高级在轨系统及在我国航天器中的应用[J]. 航天器工程,2003,12( 1) : 12-18.[3] CCSDS 102. 0 -B -5 Packet Telemetry[S]. ISO 13419,1997.

[4] Li Yanqin,Jin Shengzhen. Design of central management &control unit for onboard high - speed data handling system[J]. Journal of China university of mining & technology,2007,17( 1) : 68-72.

[5] 谭维炽,顾莹琦. CCSDS 标准星载数据系统的优化设计方法[J]. 遥测遥控,2001,22( 5) : 21-26.

[6] Virtex-Ⅱ Pro libraries guide for HDL design[M].[s. l. ]:Xilinx,2008.

[7] XPS multi-channel external memory controller ( XPS MCHEMC) ( v1. 00) [M].[s. l. ]: Xilinx,2008.[8] 张 炜,王 莹. 基于 CCSDS 高级在轨系统的遥科学空间通信链路结构研究[J]. 宇航学报,1999,20( 3) : 112-117.

[9] 别玉霞,潘成胜,蔡睿妍. AOS 虚拟信道复用技术研究与仿真[J]. 宇航学报,2011,32( 1) : 193-198.

[10] 曾连连,闫春香. AOS 虚拟信道链路控制器和 VCDU 合路器的设计实现[J]. 中国空间科学技术,2007( 2) : 17-22.[11] 田 耘,徐文波. Xilinx FPGA 开发实用教程[M]. 北京: 清华大学出版社,2008.

[12] SYNCHRONOUS DRAM -MT48LC8M32B2[M].[s. l. ]:Micron,2003