第 2 章 多媒体平台的总体方案

2.1 多媒体平台的系统构成

本文使用由 Altera 公司提供的 FPGA 芯片结合嵌入式的 Nios II 软核,利用1在软硬件相互协同方面处理数据的优势。在本文的实际设计中,我们也充分体会到这种方式带来的快捷感,它的重复配置优点使得在设计系统当中,始终选择最合适的处理器与外设来完成多媒体功能。

本系统实现的多媒体平台从大体上分为图像显示与采集功能、音频播放功能、GPS 信息接收显示功能,另外本平台还设有扩展接口包括 I/O 口和用来通讯的串口和网口。系统的硬件层是在 Quartus II 环境下将利用 SOPC builder 组件搭建的 Nios II 系统和利用 Verilog 语言编写的硬体控制器结合起来搭建而成,基于硬件层,在 Nios II IDE 环境下我们利用了μ C/OS II 系统对上述的任务进行软件上的管理和控制。本系统的整体方案如图 2-1 所示。

整个多媒体系统都是在 FPGA 资源上搭建起来的,如图 2-2 所示为本系统的系统架构图,FPGA 资源上半部用线圈出来的部分是利用 SOPC Builder 工具搭建的 Nios II 硬件系统,Altera 公司提供 SOPC Builder 组件能够完成定制 NiosII 处理器系统的工作,Nios II 软核处理器和常用的 IP 核集成在 SOPC Builder工具箱内。在设计时,用户可以自由的根据系统的需要,选择合适的外设 IP 核,通过 Nios II 软核自带的 Avalon 总线把这些 IP 核连接起来,就是一个能够满足用户需要的 SOPC 嵌入式系统。当遇到缺少系统需要的 IP 核时,用户还可以设计并自定义一个合适的 IP 核,然后添加到 SOPC Builder 工具箱的组件库中来使用。下半部分是 FPGA 中的硬体控制器,这种控制器相比于 SOPC 中的控制器,速度较快,但控制起来会相对复杂。在 SOPC 系统中 CPU 同各个控制器的数据传输互联是通过 AVALON 总线来实现的,之后,各个控制器又实现对 FPGA的外部设备进行控制,对于脱离了 AVALON 总线的硬体控制器部分,这里专门设计一条数据通道的控制器 Image_RW,将其接入 AVALON 总线,这样两部分硬件就可以结合在一起工作了。

负责图像显示和采集的控制器为 LCM 控制器和数据采集控制器,色彩格式转换模块是负责将采集到的原始 RAW 格式的数据变换成常见的 RGB 格式图像数据,一个 4 端口的硬体 SDRAM 控制器负责控制用来作为图片文件和音频文件的数据缓冲器的 SDRAM1,以上这些控制都是用硬件描述语言的方式设计完成的。Audio 控制器负责对音频解码芯片的配置和数据传输,UART 控制器负责实现串口通信,PIO 控制器实现外部 IO 的控制,SPI 控制器负责 SD 卡的驱动,SDRAM 控制器控制的是负责运行程序的 SDRAM0.以上这些控制器都是利用SOPC buider 工具完成的。

2.2 系统任务模块划分

由上面的介绍我们知道 SOPC 设计的一个很重要的特点就是软硬件设计可以协同进行,当然这就造成了开发过程中会出现问题的迭代性,也就是说,当开发的一个环节出现了问题往往不一定是当前的状态出错,很可能是流程的上游有问题,每一个环节之间都存在着千丝万缕的关系,出现问题不容易发现。

为了解决这样的问题在设计整个系统过程中,将整个系统进行模块划分是相当必要的,减少相互的依赖性,之后各个击破划,最后进行功能整合完成系统设计。另外,由于本系统是通过μ C/OS II 进行管理,其程序的最小执行单元就是任务,因此必须将整个系统进行任务的划分,以便利用操作系统进行管理。

根据多媒体平台的功能需求,首先将整个系统分成三大任务模块,分别是:

图像显示采集任务模块、音乐播放任务模块和 GPS 信息接收显示任务模块。第二步再将大的功能模块进行细分,图像显示采集模块分为 LCM 显示子模块、图像采集模块和 SD 卡驱动子模块;音乐播放模块分成解码器驱动模块和 SD 卡驱动模块;GPS 信息接收显示模块分为 UART 传输子模块和 LCD 显示模块。模块的划分如图 2-3 所示。

从中我们可以看出,将整个系统模块划分后,利用其复用性和移植性好的特点,通过对不同 IP 核和控制器的设计和组合我们就可以在很短的时间内设计出不同的多媒体功能,本系统中的 SD 卡控制器就在音乐播放功能和数码相框功能中得到了复用,无需再在不同的功能中重复设计可以直接进行控制器的移植。当对任意一项功能不再需要或者对功能要进行改变时,就可以利用 SOPC技术进行静态重构从而改变硬件平台,在很短的时间内删除该功能的控制器,释放其原来占用的逻辑资源来更换控制器实现不同的功能。同样如果我们需要其他更多的功能,也可以参照本文中的方法,利用 SOPC 方式或者在 FPGA 上直接添加硬体控制器的方式来增加其他功能。

2.3 主要模块的设计原理

上面一节中给出了整体方案的模块划分,下面分别介绍在完成各个模块时所涉及到的原理,在图像显示模块中涉及到图片解码原理和 LCM 的显示原理;音乐播放模块中涉及到音频解码原理和 SD 卡的驱动原理。

2.3.1 图像解码

在图像显示功能中,能够显示的图像格式为 JPEG、BMP 两种。BMP 是Windows 系统中标准的位图显示格式,是未经过压缩的,在读取图像数据之前不需要进行解码操作,但所占用的空间比较大;JPEG 是一种图像压缩的技术标准,一般可被分为三种编/解码系统:基于 DCT(离散余弦变换)的有损系统、基于扩展离散余弦变换的有损系统和无损压缩系统[26,27,28].由于第一类的应用场合最为广泛,所以本文也主要对这种解码方式进行讨论,下面就介绍一下基于 DCT有损压缩的 JPEG 解码的原理。

图像解码从原理上讲就是编码的逆过程,所以这里不介绍 JPEG 的编码原理直接进入解码过程。JPEG 的解码流程如图 2-4 所示。

首先是为解码做准备工作,对 JPEG 压缩码流进行预处理,提取出所需要的信息和码表,JPEG 文件包括两个部分标示符和压缩数据,标示符就相当于解码相关信息的标签,通过识别标示符才能够读出图像的长宽、量化表、哈弗曼表等各种文件的信息供给后面解码阶段使用。

第二步就是进行 Huffman 解码,MCU(最小解码单元)是压缩文件的一种存储形式。进行 Huffman 解码,就是对 MCU 进行解码,解码出来的文件包涵六个 1 维数组,其中前四个是亮度 Y 数组,后两个依次是色度 Cr 数组和色度 Cb数组,从此也可以看出解码的顺序是先进行亮度解码再开始色度解码。每一个 1维数组中又含有 64 个元素,其中第一个元素是通过 DC(直流)解码得来,后 63个元素是经过 AC(交流)解码得到。同时我们注意到这里还涉及到 Huffman 表,一般的,JPEG 文件中都有四个 Huffman 表,这个表也是为了查询码值的,Huffman 码分为码头和码值两部分,其中码值是其真实值,码头就是与 Huffman码表一一对应的标识其唯一性的信息[29,30].

接下来的一步是反量化,反量化实质上就是将解出来的 Huffman 码与其对应的量化表中的元素相乘。JPEG 文件一般有两个量化表,亮度 Y 数组对应的是第一个量化表,色度 Cr 和色度 Cb 数组对应的是第二个量化表,这里我们可以看出 JPEG 中的量化表就相当于一个算子。在进入到下一环节 IDCT 变换之前,还要对反量化后的数组进行反 Z 变换,使得一维数组变成 8*8 的二维数组以正常的顺序存储。

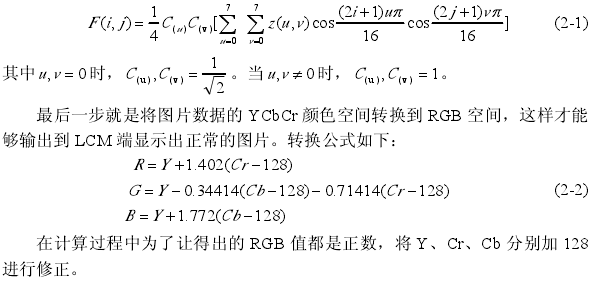

IDCT 变换是 DCT 变换的逆过程,是将上面出来的数据从频域挪到时域来,反向离散余弦变换的公式如下:

2.3.2 LCM 显示原理

在图像显示的部分本文选用的是一块 3.6 inch 的 TFT LCD,由 Toppoly 公司生产,面板型号为 TD036THEA1,分辨率为 320×240,颜色深度为 8bit,工作时钟为 18.42Mhz.LCM 的显示原理,包括传输方式、传输时序和所涉及的所有信号的作用等等。

先来从整体上对这块设备的驱动有所了解,图 2-5 可以清晰明了的体现出其驱动的整体框架。

此款显示设备拥有三种数据的传输方式分别为 RGBDummy、Serial-YUV 和Through mode.不同的方式对应着不同的时序和不同的数据格式,这里我们选择了 Through mode 方式。R、G、B 信号是由数据的输入端口依次串行进入,每个信号都是 8bit,一个 dot(像素)是有 R、G、B 三个信号组成,所以每个 dot 有24bit.LCM 面板的有效区域共有 320 列,240 行,那么一帧画面含有的 RGB数为 320×240×3.这就引出了 LCM 的场序原理,RGB 三种信号串行进入后便分别形成三个 320×240dot 的 R 场、G 场和 B 场。利用人的视觉暂留效应,整幅画面就由三个子场的叠加呈现出来,如图 2-6 所示。

2.3.3 音频解码

在音乐播放中本文选择了硬件解码的方式,音频解码芯片的型号为WM8731,它除了有较低的功耗和高的解码质量,还集成了耳机驱动器,能够利用耳机输出,增加了系统的便携性。该芯片具有独立的编程 ADC 和 DAC 采样率功能,其采样范围是 8kHz 到 96kHz,转换数据位可以调整,范围是 16 位到 32 位。

WM8731 还自带时钟模块,能够产生 44.1 kHz、48 kHz 和 96 kHz 等的采样率,本文中利用的是 48 kHz 的采样率。通过下面表格对 WM8731 的其它特性进行说明。

WM8731 内部有 11 个寄存器,本文是通过 Audio 控制器对其寄存器进行初始化配置并对数据进行控制。Audio 控制器会在第四章的模块设计部分进行详细介绍。

2.3.4 SD 卡驱动原理

在二十世纪 90 年代末期 SD 卡由闪迪、松下以及东芝公司合力研发出来的基于半导体快闪技术的存储设备,被大规模的用在例如数码相机、PAD 等移动装置上。一般的 SD 卡对应的规范是 SD Spec Ver1.0 规范,并且支持 FAT12 和FAT16 文件系统。

为了了解 SD 卡的驱动原理,首先要清楚它的内部结构,如图 2-7 所示,SD卡中最主要的部分是用来保护数据的存储内核(Memory core),卡口控制器(Cardinterface controller)与寄存器、存储内核接口(Memory core interface)和接口驱动(interface driver)相连,主机发出的外部信号就是通过卡口控制器与存储器进行访问的。此外,接口驱动模块将外部时钟的 CMD 和 DAT 信号与内部所用的时钟同步[31,32].电源检测模块(Power on detection)则是用来防止在拔插卡过程中出现短路情况。

SD 卡支持两种形式的传输:SPI 模式和 SD 模式。虽然 SPI 模式下数据传输线只有一条而 SD 模式是四位传输,但 SPI 模式的传输协议简单,易于利用软件进行控制。SD 模式下繁琐的软件实现同样会降低数据传输的速率,从折中的角度考虑本系统采用了 SPI 模式。它是一种串行的信息交换协议,利用 Nios II软核通过 avalon 总线能够与外设 SD 卡实现信息的传输[33].

利用 SPI 协议实现信息传导主要依仗四条信号线。如图 2-8 所示,Master为 SPI 的主控器,Slave 和 Slave1 是两个从外设。其中,SS_n 是片选信号,能够选择哪个外设开始工作,也就是说这种模式可以将多个外设挂在同一条avalon 总线上进行工作。SCLK 是用来提供数据传出的脉冲,控制串行数据传输的频率。MISO 和 MOSI 就是数据传输的通道,只不过传送的方向不同。如果从SD 卡中获取数据,用到的通道为 MISO 即从外设到主控的流动方向;如果是向SD 卡中写入数据,则利用 MOSI 通道,数据流向为从主控到外设[34].

2.4 本章小结

本章首先给出了多媒体平台的总体方案,为整个系统的设计划分了层次,接着从系统构成、功能模块的划分和各模块的设计原理三个方面对系统的总体方案进行了详细阐述。这一章为后面的具体的系统设计和各个模块的软硬件实现起到了很好的铺垫作用。