第 4 章 多媒体平台主要模块的实现

在第三章中已经给出了多媒体系统的任务管理框架,其中的图像显示采集子任务、音频播放子任务和 GPS 信息接收显示子任务中的主要模块设计的软硬件实现将在这一章给以详细描述。

4.1 时钟模块

在本系统中,系统时钟跟子任务的时钟不同,子任务之间的时钟也不同,所以需要利用 PLL 元件对时钟进行合理准确的分配这样才能使得任务正常运作。对系统运行速度和资源利用率的综合考虑,本系统选用了 100Mhz 的主频率,D5M 的工作频率是 25Mhz,LCM 的工作频率是 18.42Mhz,音频解码需要的频率是 18.4Mhz.因为音频解码和 LCM 的工作时钟相差很小所以可以共用同一个 PLL 产生的时钟。硬件资源中共含有两个晶振,分别是 50Mhz 和 27Mhz,我们利用 50Mhz 晶振通过 PLL 得到 100Mhz 和 25Mhz,18.4Mhz 则通过 27 Mhz获得。在 Quartus II 中,利用 Mega Wizard 中的 ALTPLL 来完成这项工作。

通过此工具我们可以设置输入时钟频率,想要得到的时钟频率、相位偏移和占空比等等,图 4-1 为配置完成后生成的 LCM 时钟模块。

特别要提到的是 SDRAM 的时钟模块,虽然 SDRAM 与系统时钟用的频率是相同的,但如果想让 SDRAM 正常工作,设置一个合适的相位偏移是至关重要的。相位偏移值,需要开发人员通过计算再加上实际操作中的经验,多次试验之后得到的数值。

SDRAM 与 FPGA 器件之间的时钟链接方式叫做源同步接口形式,就是利用同一个晶振通过同一个 PLL 产生的同频率但不同相位的关系。图 4-2 即为此种接口的模型。

这种接口形式中,FPGA 内部的部分路径延时为未知量,这部分未知延时也就是我们要计算的约束范围,也就是我们要设定的相位偏移量。

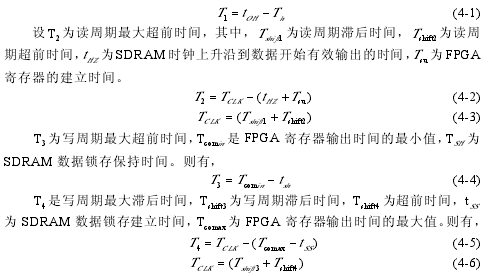

要求出相位偏移值,首先要得到四个数值,分别是读周期最大之后时间、读周期最大超前时间、写周期最大之后时间、写周期最大超前时间。下面分别列出四个参数值的计算公式。

设1T 为读周期最大之后时间,其中,OHt 为 SDRAM 数据输出有效保持时间,hT 为 FPGA 寄存器保持时间。则有,

得到1T 、2T 、3T 、4T 的值后,取1T 和3T 中的最小值作为最大滞后时间,取2T 和4T 之间的最小值作为最大超前时间,则最后的相移值由最大滞后时间和最大超前时间的平均值求得。

在上面计算当中所用到的时间数据都是在整个工程完成后进行综合,最后得出的时序约束分析中获得,但最终算出结果只能作为一个范围值,起到了缩小相位偏移范围的作用,因为计算里面没考虑到 PCB 板的线延时时间和SDRAM 从 PLL 输出到外部引脚之间的延时时间。所以在实际工程中仍要不断的调整相移值,能够定位到最佳的相移值,工作量还是比较大的,最后通过计算和实际应用中的调整,本系统的系统时钟为 100Mhz,SDRAM 的时钟相位偏移设置为-3ns 时可以正常工作。

4.2 图像显示和采集模块

图 4-3 为图像显示和采集模块中主要的几个模块与 FPGA 芯片的连接方式,具体的数据连接都展现出来了。LCM 是通过 LCM 控制器与 FPGA 相连,I2C控制器是用来配置 LCM 用的,SDRAM1 的作用是作为图片数据的缓存。

从完成 LCM 模块的显示功能的角度讲,要设计两个子模块,第一,是LCM_Controller 主控模块,第二是 I2C_Controller 驱动子模块。下面介绍这两个子模块。

4.2.1 LCM 主控制子模块

此模块实现的主要任务是完成发送数据端与外设 LCM 之间的互联,LCM的显示原理在第二章中已经讲过,这里直接进入设计过程,利用 verilog 进行控制器的编写。

首先简单说明一下设计的方法和原则,设计逻辑结构如图 4-4 所示,模块中首先要进行端口声明、数据类型的声明,这部分是与开发者对设计要求的定义紧密连接在一起的,从系统的功能确定所要用到的信号,这对整个逻辑结构起着重要的作用;接下来是模块功能或者结构描述,这部分属于控制器的主控部分,完成数据的交互方式和走向,也就是让控制器怎样进行工作的部分;最后一般是时序控制模块,这部分是整个任务的节拍器,让控制行为以何种节奏进行工作全靠这一模块。总结起来,设计的步骤大体分为:(1) 设计要求的定义。(2) 决定设计方式,编写设计代码。(3) 综合优化设计代码。(4) 处理得到网表配置 FPGA.

LCM 的主控模块就是按照这种框架设计而成,包括后面介绍的多种控制器也是按照这种模式设计,只不过是复杂度上有所区别,不过大体上是大同小异的。图 4-5 就是利用 Verilog 设计后生成的 LCM 主控模块。

图 4-5 中我们可以看出输入信号为:iRed、iGreen、iBlue、iCLK、iRST.

前三路信号分别为红、绿、蓝三路八位信号是主机端从 SD 卡获得的信号传送进来。后两位分别是控制信号时钟和全局复位信号。输出信号全部是输送到LCM 端,其中 LCM_DATA 就是通过时序控制后将三路红绿蓝信号串行传入LCM 的通道;LCM_DCLK、LCM_VSYNC 和 LCM_HSYNC 输出的信号主要是对串行输出的 LCM_DATA 在面板上的分布和时序进行控制;LCM_GRST 和LCM_SHDB 分别是低电平有效的全局复位信号和低电平有效的关断控制信号,在模块的初始化过程中直接给高电平,让 LCM 处于工作状态。

LCM 控制器的时序图如图 4-6 所示。在 LCM_VSYNC 和 LCM_HSYNC 信号都为“1”,也就是行列同步信号都为高时,数据位 LCM_DATA 开始传输到LCM 中去,并且 R、G、B 信号是串行传输,测试信号输入的 iRed、iGreen、iBlue信号分别为 0、255、127,输出的数据则是在时钟上升沿有效,串行传输,其顺序如图中所示为“GBRGB…”.

图 4-7 也是 LCM 控制器的时序图,主要表示的是行扫描信号与列扫描信号之间的关系。因为 LCM 的尺寸为 320*240,根据第二章中的显示原理,在 Z 字型扫描的过程中,在 LCM_VSYNC 一次从上升沿到下降沿的时间里,LCM_HSYNC 运行了 960 个时钟周期。以这样的计数原则完成整幅画面的像素点扫描。

4.2.2 I2C 驱动子模块

I2C 总线在系统中的作用是在主控制器与外设之间建立连接,它是一条串行总线主要有 SDA 和 SCL 两条线信号线,分别传输数据和时钟信号,总线上的地址与电路和模块一一对应,挂在总线上的模块是主控还是被控由具体模块的功能裁定,这样在工作中不同模块之间就互不影响了。

在数据传输过程中 I2C 总线会出现开始、应答、结束三种信号。如图 4-8所示,SDA 的下降沿产生开始信号,上升沿产生结束信号。当且仅当 SCL 为高时这两个信号有效。

I2C 总线数据传输的时序如图 4-9 所示,开始信号唤起器件做好准备。接着开始数据传输,以字节为传输单位,每字节固定有八位数据,每次传输的字节数不定,每传输一个字节后面都会有一个应答位。八位数据中前 7 位是数据的地址码,最后一位控制数据传输的方面。在整个数据传输的过程中,SDA 置为“1”.

如图 4-10 所示,为 LCM 模块的 I2C 驱动模块,用来输入驱动控制信号,在系统上电时对各个寄存器进行配置,使其能够正常显示。配置 TRDB_LCM需要 16 位数据。在控制器中,设计了一个 18 位的计数器,SDA 由“1”跳为“0”

且 SCL 为“1”时发送 GO 开始信号,计数器开始计数,每一次计数传输一位信号,当计数器到 8 时,传输应答信号给 ACK,接着再传输 8 位,计数器到 17时传输 END 信号,结束一次有效数据的传输。

4.2.3 图像采集模块

D5M 数据采集的时序图如图 4-11 所示,利用 FVAL(帧同步信号)和 LVAL(行同步信号)扫描数据,从图中看出,只有当这两个信号同时为高电平时,采集到的信号为有效值,所以在模块设计中要对这两个信号进行边缘检测。

如图 4-12 所示,模块中利用 X_Cont、Y_Cont 和 Frame_cont 三个计数器对行、列和帧计数,当 iFVAL 和 iLVAL 同时都为“1”且 iSTART 有效时,利用oDVAL 输出信号有效标志“1”,同时将采集到的数据传送到数据处理模块。当iEND 为“1”时停止数据采集。

4.2.4 RAW2RGB 变换子模块

上面图像采集模块采集到的图像数据,输出后是 RAWBayer 格式,不能够正常进行显示,所以这里要在采集模块后端接一个格式转换模块将其转换成RGB 格式的图像。RAWBayer 格式的图像数据奇数行是 R 和 G 信号,偶数行是B 和 G 信号。用 M 表示行数,N 表示列数,P 表示像素点,其转换原理就是提取四个像素点作为一个单元分别是 P(M,N),P(M,N-1),P(M+1,N),P(M+1,M-1)。

这里面四个点包含一个 R 信号和 B 信号,两个 G 信号,用其中的 R 和 B 作为输出的红和蓝,取两个 G 的平均值作为绿的输出。

RAW2RGB 模块如图 4-13 所示,利用它来完成格式转换,其中 iX_Cont、iY_Cont,iDATA,iDVAL 都是图像采集模块传递进来的,根据上面的讲解我们知道,转换格式过程中,会出现四中 RGB 的排列形式,模块中利用 iX_Cont 和iY_Cont 识别这四中排列方式实现数据的转换,从输出端,并行输出 R、G、B信号。

4.2.5 SDRAM 读写子模块

由于在本系统当中 LCM 工作在 18.42MHz,D5M 工作在 25MHz.而本系统的系统时钟为 100MHz,对于图像的读写操作都是在系统时钟下进行,这样一来就出现了异步时钟域的问题。因此我们利用 SDRAM 构建异步 FIFO 缓存来解决这个问题。利用 Quartus II 中的 Megawizard 工具设计一个数据宽度为 16bit,深度为 512words 的 FIFO.

Sdram_FIFO 的模块图如图 4-14 所示,当 Wrreq 信号为“1”是写有效,则开始在写时钟(wclk)下写入数据,若写满则 wrfull 输出“1”写停止,写入数据的长度由 wrusedw 输出。读数据的过程与写数据原理相同,最后通过 q 端口将数据传出。

SDRAM 读写控制器由顶层模块、接口模块、命令模块、R1、R2、W1、W2 和数据链路模块构成,如图 4-15 所示。主要为了实现:第一,刷新 SDRAM保持其中的数据;第二,仲裁主机命令,翻译将要执行的命令,使信号能与SDRAM 连接;第三,为 SDRAM 的读、写生成数据路径。

为了完成这些任务。首先,设计控制器锁相环模块的目的是将输入的 50Mhz倍频到 SDRAM 芯片所需要的 100Mhz,并且要进行移相操作,这样就能够非常准确地让采样命令信号在时钟的上升沿。第二,命令模块能够产生一个符合规定的延迟时间,然后 SDRAM 控制器会向所有的 Bank 发出预充电命令、模式寄存器装载命令和分时复用行地址和列地址等,使 SDRAM 芯片有一个确定的状态进行读与写的操作。第三,因为外部地址总线不与 SDRAM 内部地址直接相连,所以利用 SDRAM 控制器将外部地址的高位和低位分别映射到 SDRAM 的行地址和列地址。这样就能让 SDRAM 正常的读写数据了。

4.2.6 数据传输子模块

在图像显示、采集以及图像缓存等控制器都是硬体控制器,并没有连接到Nios II 软核系统中去,这样无法实现对这些控制器中的数据进行处理,因此利用这一模块作为 Nios II 系统与硬体控制器的数据通道,这个通道将作为数据缓存的 SDRAM 与 Avalon 总线相连,Nios II 软核通过 Avalon 总线就可以对相应的数据进行处理。其模块图如图 4-16 所示。

下面一步将文件添加到 SOPC Builder 中生成图片传输的 IP 核,其中比较重要的一步是对模块中各个信号类型的设置以匹配 Avolon 总线。配置界面如图4-17 所示。

其传输的时序仿真图如图 4-18 所示。从图中看出输入数据与传出的数据相同说明数据传输通道成功搭建。