摘要:国内存储器芯片快速发展, 芯片的制造工艺不断提升, 国内逻辑主流工艺发展到28 nm工艺节点, 非挥发性存储器NAND Flash发展到24 nm工艺节点。芯片被广泛应用到各种电子产品中, 集成电路芯片的ESD失效占用很大比例。它的可靠性问题越来越被关注, 静电保护电路的设计和优化显得尤为重要。提出一种有效的静电保护电路版图, 节约芯片面积, 从而实现对芯片管脚的静电保护。

关键词:集成电路设计; 静电保护; 版图设计; 寄生三极管; 静电泄放;

Abstract:With the rapid development of memory chips in China, the manufacturing process of memory chips has been improved continuously.The mainstream logic technology in China has developed to 28 nm process nodes, and the non-volatile memory NAND Flash has developed to 24 nm process nodes.Chips are widely used in various electronic products, and the ESD failure of IC chips accounts for a large proportion.Its reliability has been paid more and more attention.The design and optimization of the electrostatic protection circuit is particularly important.In this paper, an effective electrostatic protection circuit layout is proposed to save chip area and realize the electrostatic protection of chip pins.

Keyword:integrated circuit design; electrostatic protection; layout design; parasitic triode; electrostatic discharge;

1 引言

随着智能、物联网等嵌入式市场的高速发展, 芯片被广泛应用于安防、监控、车载、手机、数码相机、硬盘和超级笔记本等。应用环境差异很大, 芯片面临的一个普遍的可靠性问题, 其中失效比例至少35%的芯片是由ESD失效导致的[1], 多数是人为因素所形成[2].因此, 必须在芯片管脚添加ESD保护电路[3].

目前国内存储器工艺发展到了28 nm, 随着工艺特征尺寸的不断缩小, 集成电路的器件栅氧厚度越来越薄[4], MOS管能承受电压和电流也越来越小。因此, 从每个管脚提高芯片的抗ESD能力, 需要在每个管脚上放置了合适的ESD保护电路, 通过芯片内部ESD电路保护芯片内部器件避免被破坏[5,6].

传统的芯片使用寄生二极管导通来保护芯片, 这个寄生二极管缺点是缺少IO到VCC负静电的有效泄放通路。本文提出一种有效的ESD版图, 有效实现芯片管脚的ESD泄放, 特别是提供了有些的IO到VCC负静电泄放通路, 从而实现对芯片ESD的全模式保护。

2 传统的静电保护电路和版图设计

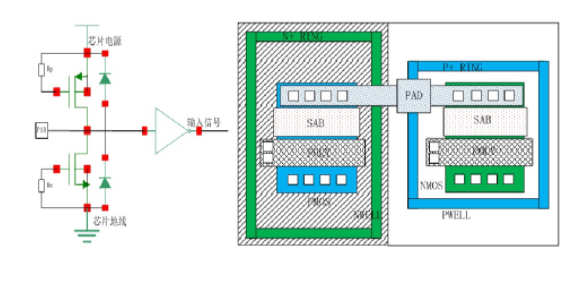

如图1所示, 传统的静电保护电路一般设计在芯片的管脚旁边, 静电保护电路由反相器输出驱动管构成, PMOS和NMOS分别通过一个电阻接到电源和地, 这样保证PMOS和NMOS在芯片正常工作时候处于关闭状态, 这种类型的静电保护电路存在二个寄生二极管, 当IO到VCC放生正静电时候, 静电通过上面的寄生二极管正向通道泄放, 当IO到GND发生正静电时候, N+ (漏端) -P+ (衬底) -N+ (源端) 形成寄生NPN, 静电通过这个寄生三极管泄放, 当IO到GND发生负静电时候, 静电通过下面的寄生二极管正向导通泄放, 当IO到VCC放生负静电时候, 静电没有合适的泄放通路。

图1 传统静电保护输入端口电路图和版图

3 优化后的保护电路的版图构造

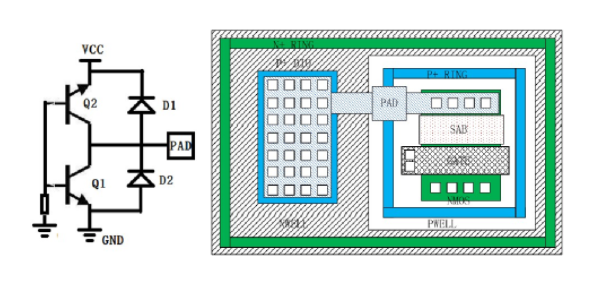

1989年T.Polgreen和P.Chatterjee解释了硅化叉指MOSFET的非均匀电流[5], 对集成电路ESD电路的改进和版图设计提出了指导性的理论依据, 如图2所示是本文采用的优化后的静电保护电路的版图, 为了防止PMOS和NMOS形成闩锁效应[7].

一是版图级防闩锁措施, 包括:加粗电源线和地线, 合理布局电源接触孔, 减小横向电流密度和串联电阻;增加多子保护环或少子保护环, 多子保护环主要可以减少衬底电阻和阱电阻, 少子环则可以预先收集少子, 减小横向NPN三极管的口值, 从而到达减小闩锁效应的目的[8].

另一种是工艺级防闩锁措施, 包括:降低少数载流子的寿命, 以减少寄生双极型晶体管的电流增益, 一般使用金掺杂或中子辐射技术;将器件制作于重掺杂衬底上的低掺杂外延层中, 重掺杂衬底提供一个收集电流的高传导路径, 降低了衬底电阻, 若在阱中加入重掺杂的P+埋层, 又可降低阱电阻[9];使用浅沟槽隔离 (STI, shallow trench isolation) 工艺, 以此减小横向NPN管的口值, 并从物理层面抑制PNP管与NPN管的耦合, 使用绝缘体上硅 (SOI, silicon on insulator) 技术, 由于绝缘层的存在, 阻断了PNPN结构的放电通路, 从根本上避免了闩锁的形成[10,11,12,13,14].

图2 优化后的静电保护电路的版图构造

具体在版图的NMOS周围增加了P+接地环和NW电源环, 优化后的版图N+ (漏端) -P+ (衬底) -N+ (源端) 形成寄生NPN.同样N+ (漏端) -P+ (衬底) -NW (NW ring) 也形成寄生NPN[15], 当PAD与GND发生ESD的时候, PAD通过NMOS的寄生二极管或者寄生三极管形成泄放通路, 从而泄放ESD电荷。当PAD与VCC发生ESD的时候, PAD通过寄生二极管或者寄生三极管形成泄放通路, 实现保护ESD的目的, 这样保证PAD对VCC打负电压时候, 有一个电流泄放通路, 同时要求在版图设计中, 需要增加NW ring接到电源上面的导线的宽度。

4 ESD电路测试

1993年ESD联合会发表了半导体器件测试的人体模型 (HBM) [16], 该模型被广泛接受, 在其他多个标准中被采用。

1994年ESD联合会发表了半导体器件测试的机器模型 (MM) [17].1995年SEMATECH建立ESD工作组以从事ESD的策略规划, 解决了ESD标准、ESD技术路线和测试设备。

1997年ESD联合会期间测试标准委员会颁布了第一份充电器件模型 (CDM) [18].

为了验证芯片ESD电路的有效性, 首先芯片的ESD测试方案, 将芯片的放电测试组合分成输入/输出-VDD/VSS, 输入/输出-输入/输出, VDD-VSS, 对于HBM静电测试, 测试所有以上的组合, 并且分别测试正向和反向ESD电压[19].

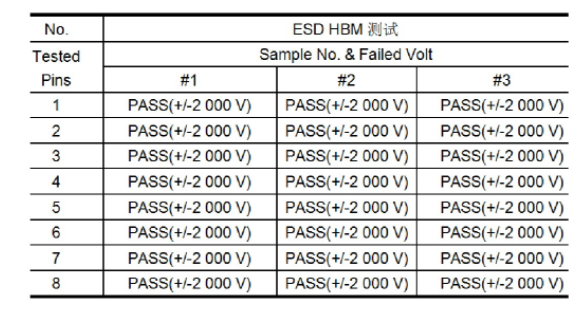

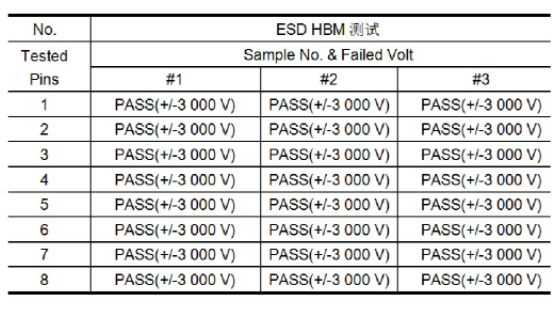

测试结果如表1和表2.表格数据表明, 优化前后的ESD结果有比较大的区别, 从而进一步细化了ESD测试方案。

方案1:检查每个管脚对电源放电的ESD放电能力;方案2:检验每个管脚对芯片地放电的ESD放电能力;方案3:检测芯片I/O到I/O的ESD放电能力;结果表明芯片管脚IO到VCC放负静电时候容易发生Fail, 测试结论和版图优化方案一致。

表1 传统的静电保护电路ESD HBM测试结果

表2 优化后的静电保护电路ESD HBM测试结果

5 结语

本文提出的这种优化后的芯片版图, 为芯片管脚提供了完整的静电泄放通路, 通过芯片实验结果表明, 本设计具有很高的可靠性, 能够有效地提高芯片ESD泄放能力, 特别适用于纳米级存储器芯片ESD输入管脚, 同时为其他集成电路芯片ESD保护电路的设计参考。

参考文献

[1]Ker Ming-Dou.Whole Chip ESD Protection DesignwithEfficientVDDtoVSSESD ClampCircuitsforSubmicronCMOS V 1 S I[J]. I E E ET r a n s. o nE l e c t r o n Devices, 1999, 46 (1) :34-37.

[2]SadikuMN, OAkujuobi.Electrostatic discharge (ESD) [J].Potentials IEEE, 2004, 22 (5) :39-41.

[3]薛忠杰。CMOS VLSI ESD保护电路设计技术[J].微电子技术, 1999 (02) :46-51.

[4]朱月珍。芯片版图设计优化技术研究[D].江苏:苏州大学, 2014.

[5]T.Polgreen, P.Chatterjee.Improving the ESD failure threshold of silicided nMOS outputtransistorsbyensuringuniform currentflow[C].Proceedingsofthe ElectrostaticOverstress/Electrostatic Discharge (EOS/ESD) Symposium, 1989;167-174.

[6]王怡飞。CMOS片上ESD保护电路设计研究[D].安徽:中国科学技术大学, 2009.

[7]栾苏珍, 刘红侠, 贾仁需, 蔡乃琼。高k介质异质栅全耗尽SOIMOSFET二维解析模型[J].物理学报, 2008 (06) :3807-3812.

[8]王彦刚, 许铭真, 谭长华, 段小蓉。超薄栅氧化层n-MOSFET软击穿后的导电机制[J].物理学报, 2005 (08) :3884-3888.

[9]张冰, 柴常春, 杨银堂。源、漏到栅距离对次亚微米ggNMOSESD保护电路鲁棒性的影响[J].物理学报, 2010, 59 (11) :8063-8070.

[10] FangRC, MollJL.Latchupmodelfor parasiticpathinbilkCMOS[J].IEEE Trans.Elec.Dev, 1984, 31 (4) :113-120.

[11]柴常春, 张冰, 杨银堂, 吴晓鹏, 王婧。一种抑制ESD保护电路闩锁效应的版图研究[J].电路与系统学报, 2013, 18 (01) :332-335+342.

[12]朱琪, 华梦琪。CMOS工艺中抗闩锁技术的研究[J].电子与封装, 2014, 14 (04) :34-37.

[13]钱敏。CMOS集成电路闩锁效应的形成机理和对抗措施研究[J].苏州大学学报 (自然科学版) , 2003 (04) :31-38.

[14]钱敏, 黄秋萍, 李文石。CMOS集成电路抗闩锁策略研究[J].集成电路应用, 2005 (02) :10-14.

[15] AMERASEERAADUURYC.ESDinSilicon IntegratedCircuits[M].USAohniley&Sons, 2002.

[16]ESDAssociationS5.1, 1993, HBM-ESDSensitivityTesting:Humanbody model (HBM) -Component level[S].1993.

[17]ESDAssociationS5.2, 1994, MM-ESD Sensitivity Testing:Machine model (MM) 一Component level[S].1994.

[18]ESDAssociationS5.3, 1997, CDM-ESD SensitivityTesting:Chargeddevice model (CDM) -Component level[S].1997.

[19]侯文煜。集成电路ESD失效机理和ESD防护电路研究[D].陕西:西安电子科技大学, 2015.

随着半导体工业进入到超深亚微米时代, 工艺越来越复杂, 数字集成电路设计规模越来越大, 导致在版图设计过程中未知的、不可控的因素逐渐增多, 遇到了大量的时序、信号完整性、可制造性和可靠性等方面的问题....

导1预判电路是浮点运算中不可缺少的一部分, 其原理是将先导1位置的判断与加/减法运算同步进行, 而不必等到加/减法运算完成以后再根据其结果进行判定。...

集成电路设计的流程通常包含系统设计, 逻辑设计, 电路设计, 版图设计, 以及之后的仿真。版图设计在整个设计流程的最后阶段, 它是将电路设计转换为物理版图的设计过程, 它的主要内容是根据电路设计合理的规划布局和布线。...

版图设计是一个电路设计思想实现为物理版图的过程,是设计阶段的最后过程。现如今CMOS工艺实现过程复杂度和运作效率越来越高,工作电压呈现一个下降趋势。...

版图设计是集成电路版图的最后一个设计环节, 其作用a是起到收尾作用。由于这是系统中最后的一个环节, 因此, 其设计的开展是在其前面的系统设计、逻辑设计以及电路设计等基础上进行的。...

存储器产品在集成电路市场中一直占据着较大的份额。作为主流非易失存储器的Flash是一种基于电荷存储的非 易失性存 储器,采用具有 浮栅的MOS管来存储电荷。...