摘要:随着当前我国信息技术的不断发展, 集成电路的设计和应用水平越来越高, 但其在体积的设计方面却呈现越来越小的趋势, 这便对其电路版图设计的技巧提出了更高的要求。设计者需要考虑系统配置、电路形式、版图设计以及工艺技术等各方面的设计, 才能符合产品的设计要求。这也体现了版图设计在整个集成电路中的重要性。本文主要分析探讨了集成电路版图设计的相关技巧, 提出相关版图设计方法与规则, 以作为相关参考。

关键词:集成电路; 版图设计; 技巧分析;

一、集成电路版图设计概述

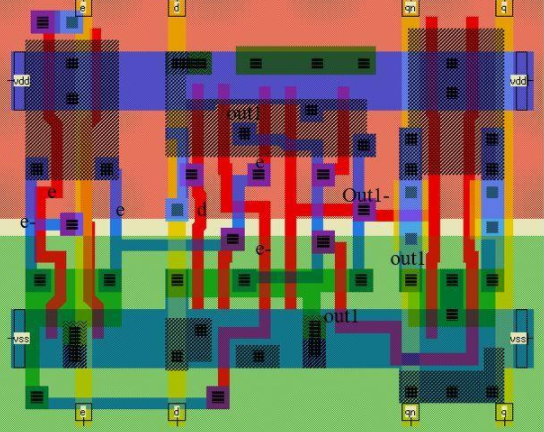

版图设计是集成电路版图的最后一个设计环节, 其作用a是起到收尾作用。由于这是系统中最后的一个环节, 因此, 其设计的开展是在其前面的系统设计、逻辑设计以及电路设计等基础上进行的。其设计的主要内容是对版图进行设计和对线路进行布局。这要求设计者具备高水平的专业技术水平, 熟悉各种电子元件的性能、作用以及工艺制造的技术方法等, 只有具备这样才能实现以最少的成本和最小的芯片面积获取集成电路版图的最优设计。就目前来看, 集成电路版图设计最常用的软件是Cadence, 其功能较强大, 性能稳定而可靠, 且应用起来十分方便[1].

二、版图设计方法与规则

在版图的设计中, 大致可以将其分为以下几种设计方法:以自动化为划分标准, 可以将版图设计方法划分为手工设计以及自动设计两个部分。手工设计是指利用版图设计工具通过编辑基本图形的方式来得到晶体管和其他基本元件的版图, 再以逐层绘图的方式来实现整个集成电路板图的设计, 计算机所起到的只是辅助作用, 其优势是能够以自由故事的版图设计规则, 将每个元件及其内连接方式安排紧凑, 提高系统的集成度, 利于降低生产成本。而自动设计的部分在只要将设计电路图的网表输入到某个平台上, 再加上一些诸如速度、功耗和面积等约束条件, 最终实现集成电路版图设计。但以布局模块的划分作为标准, 可以将其分为全定制与半定制两种。在设计规则方面, 则需要规定图形之间的间距, 但由于每个设计公司的工艺设计标准有所不同, 因此, 要解决其间距不统一的问题, 就需要使用高级的CAD工具来将其间距控制到最小程度。该工具能够跟着线性变化的程度变化, 能够灵活方便地在兼容工具之间进行转换, 但该方式的线性度只能适用于一定的范围, 不能解决超出尺寸和紧密性减少的问题, 这是其不足之处。

三、集成电路版图具体设计分析

(一) 版图的全局规划设计

对于集成电路的版图设计来说, 全局设计是关键步骤, 这个环节与相关元件所处的位置与布局有关系, 这一布局设计方式与已经成型的电路图十分相似, 需要根据每个模块的面积, 以做出相应的调整, 并以其合理的、紧凑的方式结合起来。其布局是指将设计好的功能模块合理地安排在芯片上, 并将各自的位置规划好, 这样有利于将每个组元以及整个设计的尺寸进行规划和设计, 提高模块和组元在芯片之间的位置的精确度, 这是保证芯片面积尽量最小的前提条件, 并最终实现布线的成功。但还需要注意全局设计中的焊盘设计, 这是满足电路内部信号相互连接的关键, 能够最大程度上实现芯片成本的降低。因此, 在全局设计中, 应将模块的设计和焊盘的布局进行充分考虑。当前比较普遍使用的集成电路版图设计工具有Cadence、Synopsys、Tanner、Mentor Graphics以及Avanti等, 这些工具中又数Cadence最优, 主要体现在版图电路的设计、自动布局与布线以及仿真、验证等方面占有的巨大优势, 十分适合于集成电路的版图设计模式[2].

(二) 分层设计

分层设计是建立在全局设计的基础之上的, 因此, 只有对电路全局设计掌控好, 才能更好地进行分层设计。首先, 需要在全局设计模式之下, 需要将集成电路中的全部模块和所有元件进行合理设计。其次, 在进行合理设计的基础上, 将集成电路划分为几个不相同的单元, 并对每个不同的单元和模块进行分层设计, 这样才能做好整个集成电路的版图设计。在进行布线时, 通常考虑到布线的复杂性, 也会将布线分两部的方式来完成, 即分为总体布线和详细布线两种。总体布线需要将线网分配于合适的区域范围之内, 才能确保较高的布通率。而详细布线正是在这个基础上进行的, 有利于最终确定其连线的具体位置。采用分步布线的方式能够有效避免局部拥挤, 简化布线步骤, 提高布线的成功概率。在进行分层设计时, 需要注意的是, 设计者须依照大模块-小模块的顺序来进行设计, 才能保证每一个模块和单元的设计更加合理有效, 从而提高整体的版图设计质量。

(三) 版图的检查分析

由于版图的设计过程是一个不断优化的过程, 因此, 为了切实得到一个较好的设计方式, 需要对版图设计的总体布线和布局进行反复地检查和验证, 这些是必不可少的环节。版图设计三阶段中每一个后续步骤都是以前一个步骤的结果为依据的, 因此, 在前一个布局设计中需要充分考虑到后续阶段的布局, 以保证前后阶段的布局设计相一致。这样各个阶段相互影响、相互作用, 对版图进行综合考虑和设计, 实行全盘优化, 才能够获得一个良好的布局结果。具体来说, 版图的检查步骤如下:首先, 是运用DRC的识别能力, 对图形、文件等按照相关程序和规则进行检查, 将错误标记出来, 给出合理的解释。其次, 是对线路的开路、短路等进行检查, 将错误控制在最短连接通路之中。第三, 是运用LVS来比较不同的版图和原理图, 发现并修改其中不一致的地方, 指导其版图的电路设计图相一致。第四, 是对版图进行进一步的修改, 如检查其各项连接是否正常, 得到的结果是否确实可靠, 各项器件的类型与其命名是否相一致等, 接着在认真研究设计图的基础上, 做好DRC的改错工作。最后, 是从版图的面积的最小化、运行速度的最优化以及电路的整体性能等方面出发, 并注意提取整个电路的延时信息与网表, 进行最后的仿真验证, 这样才算完成了对版图的优化验证。

四、结语

综上所述, 集成电路的版图设计与优化需要以一定的方法与规则为基础, 从全局设计和分层设计两个方面着手, 进行仔细地分析与探讨, 才能做好版图的布局布线工作, 以及其后期的版图检查验证工作。这整个过程中, 设计者自身需要有强硬的专业知识和技术, 熟悉集成电路的版图设计方式和规则, 并能够熟练使用版图设计工具, 才能真正做好集成电路的版图设计工作, 促进集成电路版图设计水平的提高。

参考文献

[1]孙丽莉, 史小波。集成电路版图设计技巧[J].电子世界, 2016, (9) :81-82.

[2]齐俊伟。集成电路版图设计的技巧[J].黑龙江科技信息, 2014, (19) :114.

随着半导体工业进入到超深亚微米时代, 工艺越来越复杂, 数字集成电路设计规模越来越大, 导致在版图设计过程中未知的、不可控的因素逐渐增多, 遇到了大量的时序、信号完整性、可制造性和可靠性等方面的问题....

本文便对灯光布置的特点、原则以及技巧进行研究,为相关部门提供参考性建议。...

导1预判电路是浮点运算中不可缺少的一部分, 其原理是将先导1位置的判断与加/减法运算同步进行, 而不必等到加/减法运算完成以后再根据其结果进行判定。...

在集成电路厂房的设计中,设计人员还需要针对该厂房建筑所在的周边环境开展详细的调研,将设计思想与调研结论充分结合,以避免不必要的浪费,降低对资源的消耗,不断提高资源的再生指标。...

随着智能、物联网等嵌入式市场的高速发展, 芯片被广泛应用于安防、监控、车载、手机、数码相机、硬盘和超级笔记本等。...

集成电路设计的流程通常包含系统设计, 逻辑设计, 电路设计, 版图设计, 以及之后的仿真。版图设计在整个设计流程的最后阶段, 它是将电路设计转换为物理版图的设计过程, 它的主要内容是根据电路设计合理的规划布局和布线。...

版图设计是一个电路设计思想实现为物理版图的过程,是设计阶段的最后过程。现如今CMOS工艺实现过程复杂度和运作效率越来越高,工作电压呈现一个下降趋势。...

在版图设计中重要。在集成电路芯片的版图的设计过程中,对于金属层存在着金属线资源分布不均匀的问题,这些在电路设计中是体现不出来的,但是在芯片的生产过程中,由于生产工艺的关系就会出现问题。...

存储器产品在集成电路市场中一直占据着较大的份额。作为主流非易失存储器的Flash是一种基于电荷存储的非 易失性存 储器,采用具有 浮栅的MOS管来存储电荷。...