摘要:介绍两种流片方式生产的晶圆, 即单项目晶圆和多项目晶圆, 阐述单项目晶圆和多项目晶圆的区别, 并以芯片产业化测试的角度提出了多项目晶圆在流片之前进行版图排版设计注意事项, 多项目晶圆排版可根据此文建议方式灵活运用。

关键词:多项目晶圆; 单项目晶圆; 版图; wafer;

Abstract:This paper introduces two kinds of production mode: single silicon wafer project wafer and multi project wafer. It describes the difference between single project and multi project wafer wafer. And the chip industry test is proposed for multi project wafer layout design considerations in the process before. Multi project wafer layout can be flexibly used in accordance with the proposed method.

Keyword:multi project wafer; single wafer; layout;

1 引文

通常独立流片晶圆为单项目晶圆, 但特殊情况下, 为了节省流片费用, 同时生产数量较多的芯片, 采用单片wafer上安排多种芯片的流片形式, 即多项目晶圆独立流片。对于单项目晶圆, 由于整个wafer上只有一个项目, 版图拼版形式较为简单规整, 所有芯片大小相同, 所有的划片道均相同;对于多项目晶圆来说, 单片wafer上包含2种或者2种以上的芯片, 且各个芯片的大小有可能不相同, 因此, 各种芯片的版图拼版方式则存在多样性。

本文结合独立流片多项目晶圆实践案例, 介绍了多项目晶圆概念, 给出了版图排版建议方式, 对多项目晶圆的了解和版图排版设计有一定的指导作用。

2 单项目晶圆和多项目晶圆

晶圆安排独立流片通常涉及到两种方式:单项目晶圆和多项目晶圆。

2.1 单项目晶圆

独立流片返回的晶圆, 单片wafer上仅包含唯一芯片的一个方案, 整个wafer上具有相同宽度的划片道, 任何一个芯片的X和Y方向边缘均规则的排列在wafer上, 这是最常见的一种流片方式, 适用于大批量芯片供货及应用, 此类晶圆通常叫做单项目晶圆。

2.2 多项目晶圆

独立流片返回的晶圆, 单片wafer由若干个相同的Block重复排列而成, 每个Block又有规律地排列了两种或者两种以上的芯片, 以这种方式进行流片的晶圆称为多项目独立流片晶圆。显而易见, 多项目晶圆安排独立流片可以在保障产出多个种类、较大数量的芯片的条件下, 减少流片的费用。实际操作过程中, 根据各个芯片应用需求量的大小不同, 可以在光罩掩膜版排列的Block上多放置一些需求数量较大的芯片。多项目晶圆独立流片不仅节省了流片费用, 同时保障了一定量芯片产出。具体单片wafer包含多少芯片, 不仅与最小Block排列规则有关, 亦与芯片大小、划片道等因素有关。

2.3 多项目晶圆最小Blcok中包含子Block模式

多项目晶圆wafer上的最小Block中, 如果一个Block内部包含多个某类型芯片, 那么该类型芯片出现在Block内部必须具有一定的规律性, 以保障在一个Block块内部出现的重复芯片各自也可以组成子Block模块, 最小Block模块可以由多个子Block模块组成。

晶圆在进行中测时, 需要以芯片上的某一块面积作为图像识别的mode, 该mode要求在芯片上有行有列, 明亮相间。而多项目晶圆光罩掩膜版上最小Block中的子Block模块是相对于待测试芯片而言的, 子Block模块内部除待测试芯片之外, 其余芯片作为黑盒处理或者作为待测试芯片的一部分处理, 子Block模块唯一性识别mode仅仅以待测芯片内部作为识别mode区域。

3 多项目晶圆版图拼版方式

无论单项目晶圆还是多项目晶圆, 流片完成之后, 通常都需要进行探针台中测测试。为了顺利完成多项目晶圆中测测试, 且中测之后map文件可以应用于后续加工工艺, 多项目晶圆拼版必须满足一定的规则。本节将根据多项目晶圆中测的两种测试方法, 阐述多项目晶圆上两种或者两种以上的芯片排列及拼版方式。

3.1 采用最小Block法中测的多项目晶圆拼版方式

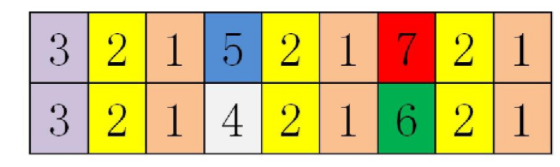

为了清晰说明以最小Block法处理多项目晶圆Device建立方法, 以图1所示多项目晶圆独立流片为例说明。图1中所示包含了7种芯片, 每个芯片尺寸各不相同, 但是为了采用多项目晶圆进行独立流片, 7个芯片中以最大的芯片面积作为基准, 其余芯片全部按照此芯片大小进行布版, 若芯片较小, 那么芯片周围填充金属, 最终使得每个芯片的大小均相同, 本例独立流片多项目晶圆, 其每个芯片的大小为1 060μm×820μm, 划片槽宽度双方向均为80μm.

图1 多项目晶圆上包含7个芯片的最小Block示例

采用最小Block法进行探针台中测时, 多项目晶圆上的芯片从外观上看必须大小相同, 整个wafer上的划片道尺寸唯一。

3.2 采用Group index方法中测时多项目晶圆拼版方式

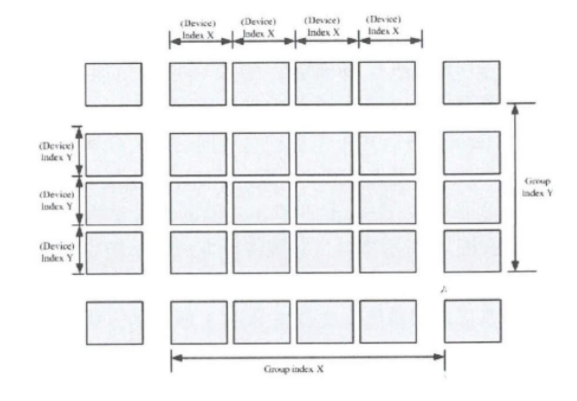

根据探针台测试时Chuck台运行的规则, 探针台采用Group index方式进行中测时, 其步长及划片道设置有一些基本规则, 图2所示为最普通的按照Group index方式进行中测时芯片步长、相对位置及划片道示意图。

从图2可以看出, 芯片之间可以出现规则的两种不同宽度的划片道, 即围绕Group index是一种宽度的划片道, group内部是另一种宽度的划片道, 但绝对不允许在同一片晶圆上出现两个以上的划片道宽度, 实际应用中通常采用相同的划片道, 便于测试识别, 操作起来也更加方便[2].

图2 Group index方式中测时步长及划片道设置

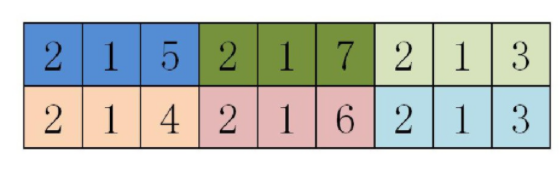

图3 两种划片道宽度条件下采用Group index方式拼版要求

从以上分析可知, 采用Group index方式建立Device安排中测时, wafer上版图排版时有如下规则需要遵守:

(1) wafer上的芯片划片道可以有2个, 但不能超过2个, 而且两个划片道分布在Group index内部和外围。

(2) wafer上的各种芯片行或者列要求必须排列整齐, 芯片大小相同, 如果芯片大小不同, 可以将较小的芯片外围填充金属, 最终使得每个芯片的大小均相同。

(3) 如果设计允许的话, 划片道最好全部一致, 可方便测试人员进行探针台中测Device的建立;所有划片道相同, Group index可以看做最小子Block进行设置, 测试灵活性较大。

(4) Group index使用规定, Group index作为一个整体, 每个wafer上X方向或者Y方向, 必须包含5个或者更多的Group index, 否则不能使用Group index功能。

(5) 由于Group index功能的存在, 使得Group内部的芯片均可进行cp测试。如果wafer上Group外围划片道宽度和Group内部的划片道宽度不同, 那么所有的Group在其左下角必须有相同的芯片位置做参考, 每个Group是在wafer上最小子Block重复单元。

因此, 如果Group内部和外围的划片道宽度不同, 那么图1所示多项目晶圆拼版方式将不能安排探针台中测。如果仅仅需要测试1号方案和2号方案, 那么需要将版图排版方式调整为图3所示的方式。图3的拼版方式中, 最小子Block的左下角芯片相同。

4 版图排版设计其他注意事项

除了上文所述的多项目晶圆多个芯片版图排版方式要求外, 为了满足芯片加工过程中各个工艺阶段中测结果的需求, 版图排版设计还有一些需要注意的事项, 具体如下:

(1) 无论是采用最小Block方式还是采用Group index方式建立Device进行探针台中测, wafer上设置一些"L"状的标记非常重要, 不仅对芯片中测前建立Device的操作人员提供方便, 同时也对后续加工工艺工程师准确识别各种芯片提供帮助[3].

(2) 多项目晶圆, 不同的芯片PAD形状, 在归属上应该一致。Wafer上通常出现八角型和方型两种pad, 因此, 最好可以将RF脚和GND脚所使用的pad形状固定。在本例多项目晶圆中, 发现两种不同的芯片上的pad, 一个使用方形作为RF脚, 另一个使用八角形作为RF脚。在同一片wafer上, 针对两种或者两种以上的芯片, Pad类型不同则使用不同的形状标记, 目的是为了方便各个加工阶段进行准确识别芯片。

(3) 从理论上讲, 只要wafer满足Group的行列数量规定, 且由多个规则的Group index组成, 单个Group由规则的N种芯片组成, 那么都可以使用Group index方式建立Device, 探针台亦可以实现中测测试;但是, 从芯片实际后封装工艺的加工情况考虑, 通常只安排单个Group由两个芯片组成, 同时为两种芯片的map图工艺摘片, 单个Block超过2个芯片通常采用盲封。

(4) 如果多项目晶圆芯片后续通过倒封装工艺提取芯片, 那么此多项目晶圆必须采用Group index方式建立的map图, 每个Device将对非待测芯片进行mark或者skip处理, 最终每种芯片将产生一个对应的map图, 此map图将用于后封装摘片工艺。

5 结语

本文阐述了多项目晶圆和单项目晶圆的区别, 从芯片产业化测试可行性的角度考虑, 分析了多项目晶圆上各种类芯片在版图上的处理方式, 给出了各个芯片组成的最小Block在版图上可行的拼版方式, 最后总结了版图拼版的基本方法及注意事项。

参考文献

[1] 杨跃胜。探针台测试操作指南V1.2 (20140514) [Z].2014.5

[2]USER'S MANUAL_OPERATION[M].TOKYOSEIMITSUCO., LTD.

[3] 杨跃胜。芯片标记技术[Z].20120803

随着半导体工业进入到超深亚微米时代, 工艺越来越复杂, 数字集成电路设计规模越来越大, 导致在版图设计过程中未知的、不可控的因素逐渐增多, 遇到了大量的时序、信号完整性、可制造性和可靠性等方面的问题....

导1预判电路是浮点运算中不可缺少的一部分, 其原理是将先导1位置的判断与加/减法运算同步进行, 而不必等到加/减法运算完成以后再根据其结果进行判定。...

每个企业厂区的地下都布置着很多管线, 或疏或密, 对于一个北方石化企业来说, 生产区地下管线将是更为密集, 管理起来越发困难。...

随着智能、物联网等嵌入式市场的高速发展, 芯片被广泛应用于安防、监控、车载、手机、数码相机、硬盘和超级笔记本等。...

集成电路设计的流程通常包含系统设计, 逻辑设计, 电路设计, 版图设计, 以及之后的仿真。版图设计在整个设计流程的最后阶段, 它是将电路设计转换为物理版图的设计过程, 它的主要内容是根据电路设计合理的规划布局和布线。...

版图设计是一个电路设计思想实现为物理版图的过程,是设计阶段的最后过程。现如今CMOS工艺实现过程复杂度和运作效率越来越高,工作电压呈现一个下降趋势。...

在版图设计中重要。在集成电路芯片的版图的设计过程中,对于金属层存在着金属线资源分布不均匀的问题,这些在电路设计中是体现不出来的,但是在芯片的生产过程中,由于生产工艺的关系就会出现问题。...

版图设计是集成电路版图的最后一个设计环节, 其作用a是起到收尾作用。由于这是系统中最后的一个环节, 因此, 其设计的开展是在其前面的系统设计、逻辑设计以及电路设计等基础上进行的。...

存储器产品在集成电路市场中一直占据着较大的份额。作为主流非易失存储器的Flash是一种基于电荷存储的非 易失性存 储器,采用具有 浮栅的MOS管来存储电荷。...